🧱 openlane2-sram

Macro-Aware Physical Design with OpenLane2 (SRAM Hard Macro Integration)

🔗 Links

| Language | GitHub Pages 🌐 | GitHub 💻 |

|---|---|---|

| 🇺🇸 English |  |

|

📌 Project Overview

This repository demonstrates macro-aware physical design using OpenLane2 (v2)

by integrating an SRAM hard macro into a complete RTL → GDS flow.

The focus is not SRAM design, but realistic integration of a hard macro

(LEF / GDS / blackbox) into an OpenLane2-based physical design flow.

🎯 Project Goal

- ✅ Use OpenLane2 correctly and reproducibly

- 🧱 Treat SRAM as an external hard macro

- 🗺 Complete floorplanning, placement, and routing

- 📦 Generate a final GDS including the SRAM macro

- 📘 Document the entire process for reuse and education

📐 Scope

✔ What this project does

- 🛠 Install and run OpenLane2 (non-destructive setup)

- ▶ Execute a baseline OpenLane2 flow (standard-cell only)

- 🧠 Integrate an SRAM hard macro:

- Verilog blackbox

- LEF / GDS inclusion

- Fixed macro placement

- 🔗 Complete routing and GDS generation

- 📚 Provide step-by-step documentation

✖ What this project does NOT do

- ❌ Design or synthesize an SRAM

- ❌ Distribute proprietary SRAM macro files

- ❌ Perform full commercial sign-off (LVS / advanced DRC)

- ❌ Support legacy OpenLane (v1)

📚 Documentation Guide

Please read in the following order:

-

📘 Project Plan

Scope definition, milestones (M0–M3), and completion criteria. -

🛠 Environment Setup

OpenLane2 installation, Python environment, and PDK handling. -

▶ Baseline OpenLane2 Flow

Minimal RTL → GDS run without macros. -

🧠 SRAM Macro Integration

Blackbox declaration, LEF/GDS usage, and macro placement strategy. -

📊 Results and Observations

Final GDS, warnings, limitations, and lessons learned.

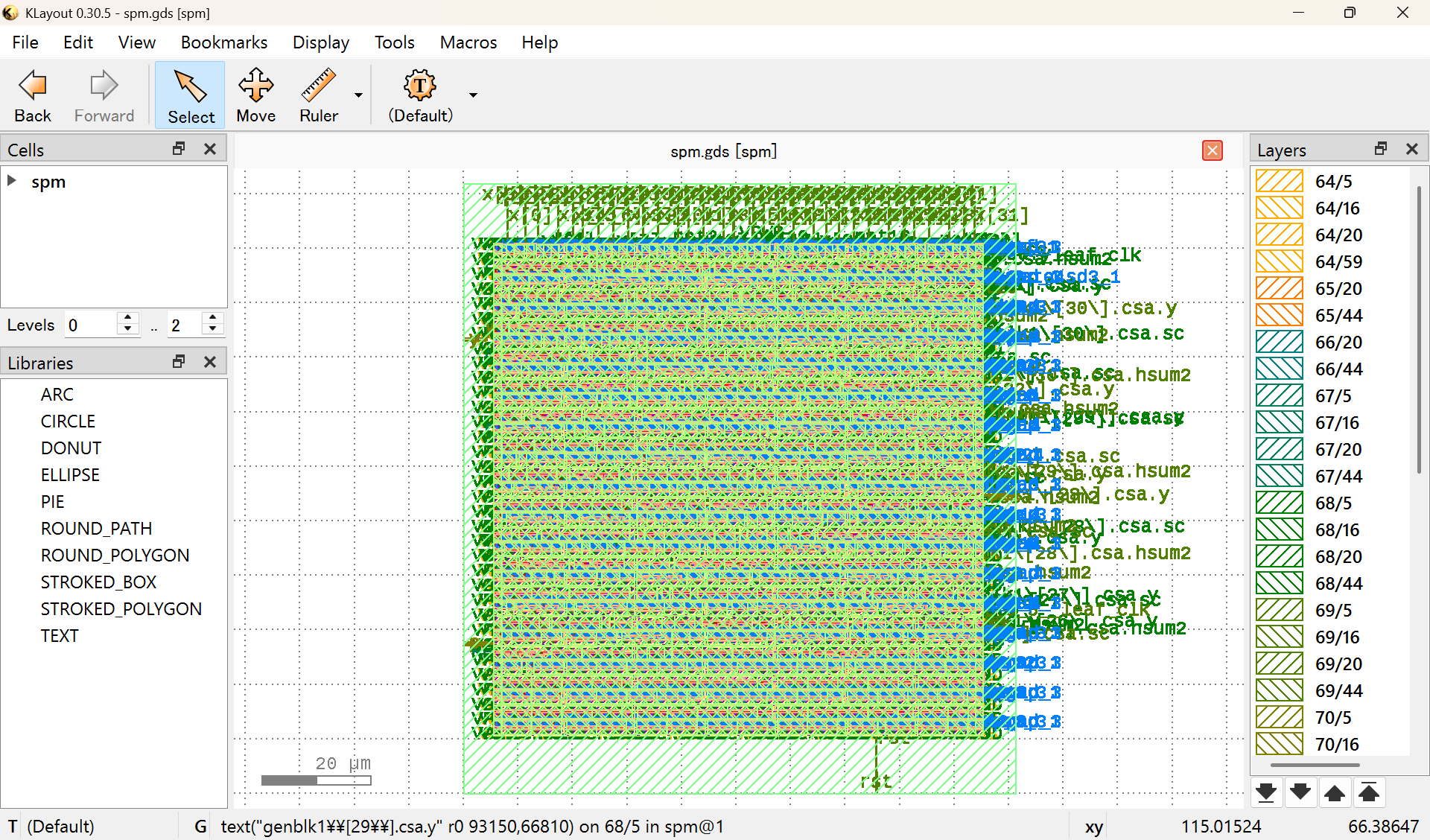

🖼 Figure 1: SRAM Macro Block-Level View

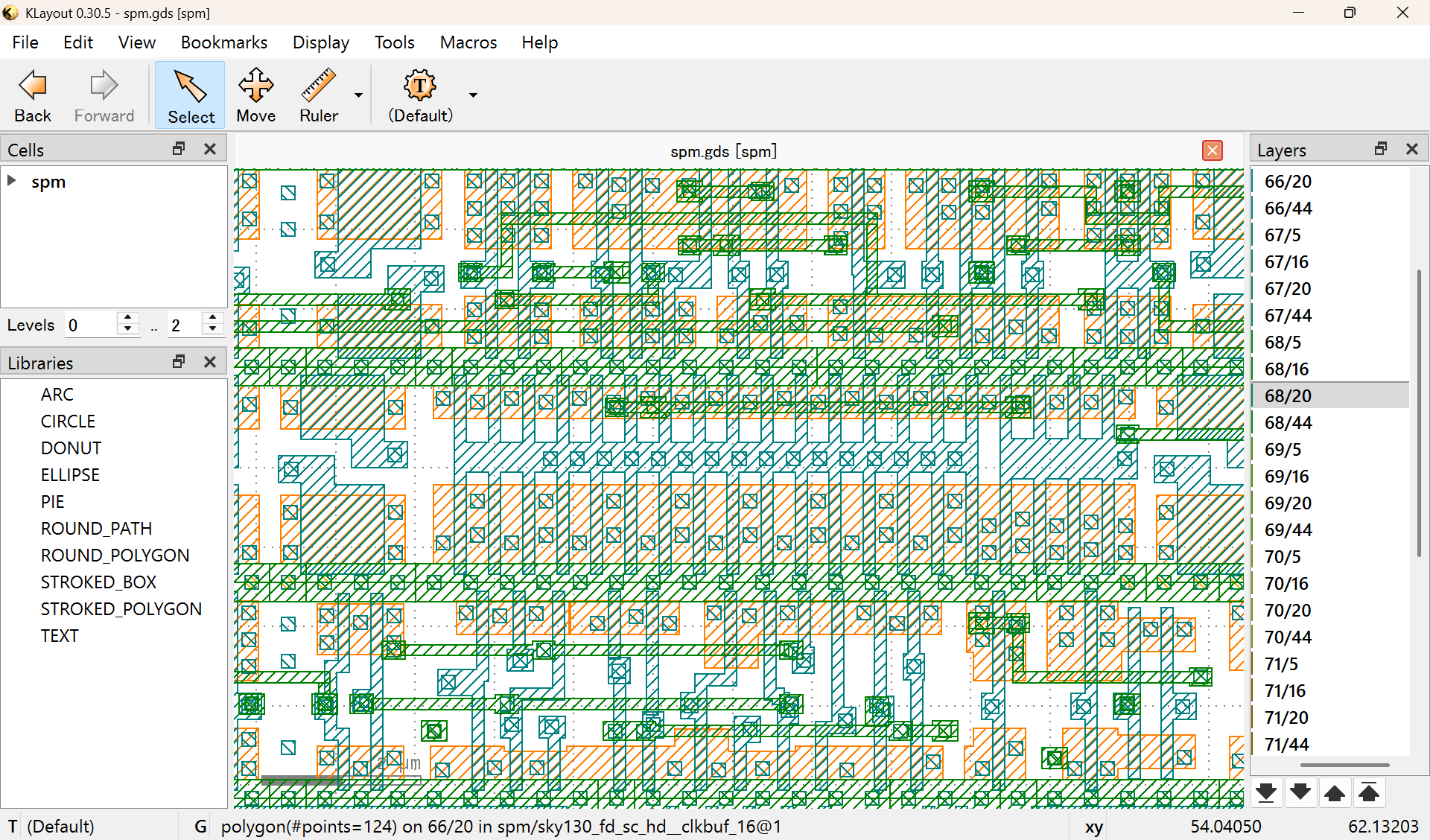

🔬 Figure 2: Standard-Cell / Transistor-Level View Around SRAM

🗂 Repository Structure

This repository is structured to clearly separate

documentation, design inputs, and generated artifacts.

📁 Top-Level

openlane2-sram/

├─ README.md

├─ docs/

│ ├─ 00_plan.md # Project scope and milestones

│ ├─ 10_env.md # Environment setup (OpenLane2, PDK)

│ ├─ 20_openlane2.md # Baseline OpenLane2 flow (no macros)

│ ├─ 30_macro_sram.md # SRAM hard macro integration

│ └─ 40_results.md # Results, warnings, lessons learned

│

├─ designs/

│ └─ spm/

│ ├─ config.json # Main OpenLane2 configuration

│ ├─ run_config.json # Runtime / flow options

│ ├─ pin_order.cfg # IO pin ordering

│ └─ src/

│ ├─ spm.v # Top-level RTL

│ └─ spm.sdc # Timing constraints

│

├─ runs/ # Generated by OpenLane2 (gitignored)

│ └─ RUN_YYYY-MM-DD_* # Per-run artifacts (logs, DEF, GDS)

│

└─ .gitignore

🏁 Milestones

- M0 🛠: OpenLane2 installation

- M1 ▶: Baseline RTL → GDS flow

- M2 🧱: SRAM macro integration and floorplanning

- M3 📦: Routing completion and final GDS generation

Each milestone produces verifiable artifacts.

🧠 SRAM Macro Policy

SRAM macros are treated strictly as external hard macros.

- 🚫 No SRAM GDS / LEF files are included

- 🔗 Users must provide or link their own macros

- 📘 This repository documents integration methodology only

This keeps the project license-safe and reusable.

🧩 PDK

- 🎯 Target PDK: Sky130

- 🚫 PDK files are not included

- 💻 The flow assumes an existing local PDK installation

🎓 Intended Audience

- 🛠 OpenLane2 / OpenROAD users moving beyond standard-cell-only flows

- 🧠 Engineers learning macro-aware floorplanning

- 📘 Educators preparing realistic physical design examples

📊 Status

✔️ Baseline flow and SRAM macro integration verified

This repository evolves incrementally with emphasis on

clarity, reproducibility, and realistic physical design practice.

👤 Author

📄 License

| 📌 Item | License | Description |

|---|---|---|

| Source Code | MIT License | Free to use, modify, and redistribute |

| Text Materials | CC BY 4.0 or CC BY-SA 4.0 | Attribution required; share-alike applies for BY-SA |

| Figures & Diagrams | CC BY-NC 4.0 | Non-commercial use only |

| External References | Follow the original license | Cite the original source properly |

💬 Feedback

Suggestions, improvements, and discussions are welcome via GitHub Discussions.