🧱 【ハードウエア:03】aitl-physical-reference v2 : 物理ループ参照 ― 制御の前に凍結すべき銅と電流

topics: [“hardware”, “kicad”, “aitl”, “architecture”, “pcb”]

🧩 【AITL】v2 物理ループ参照

― 制御の前に凍結すべき銅と電流

この記事は aitl-physical-reference v2 を解説する技術記事です。

結論から言います。

v2 は「制御できるもの」を増やす版ではありません。

制御してはならない物理(銅・電流・外形)を凍結する版です。

❓ なぜ v2 が必要か

制御・FSM・PID・AI を議論するとき、

私たちは無意識にこう仮定しています。

- 電圧は出る

- 電流は流れる

- LED は点く

- GND は GND である

しかし、それらは論理ではなく物理の事実です。

v2 は次の問いにだけ答えるために存在します。

「制御を一切入れずに、電圧と電流の“完全なループ”を凍結すると何が残るか?」

🔁 v0 / v1 / v2 の違い(整理)

| Version | 役割 |

|---|---|

| v0 | 受動的な物理部品の寄せ集め |

| v1 | 論理 ↔ 物理の意味定義 |

| v2 | 実行可能な物理ループ(DRC clean) |

| v3 | 制御(FSM / PID)の挿入 |

v1 が

「このピンが High とは何か」

を定義したのに対し、

v2 は

「その意味が成立する“銅の形”とは何か」

を凍結します。

🖼 v2 Figures (Embedded)

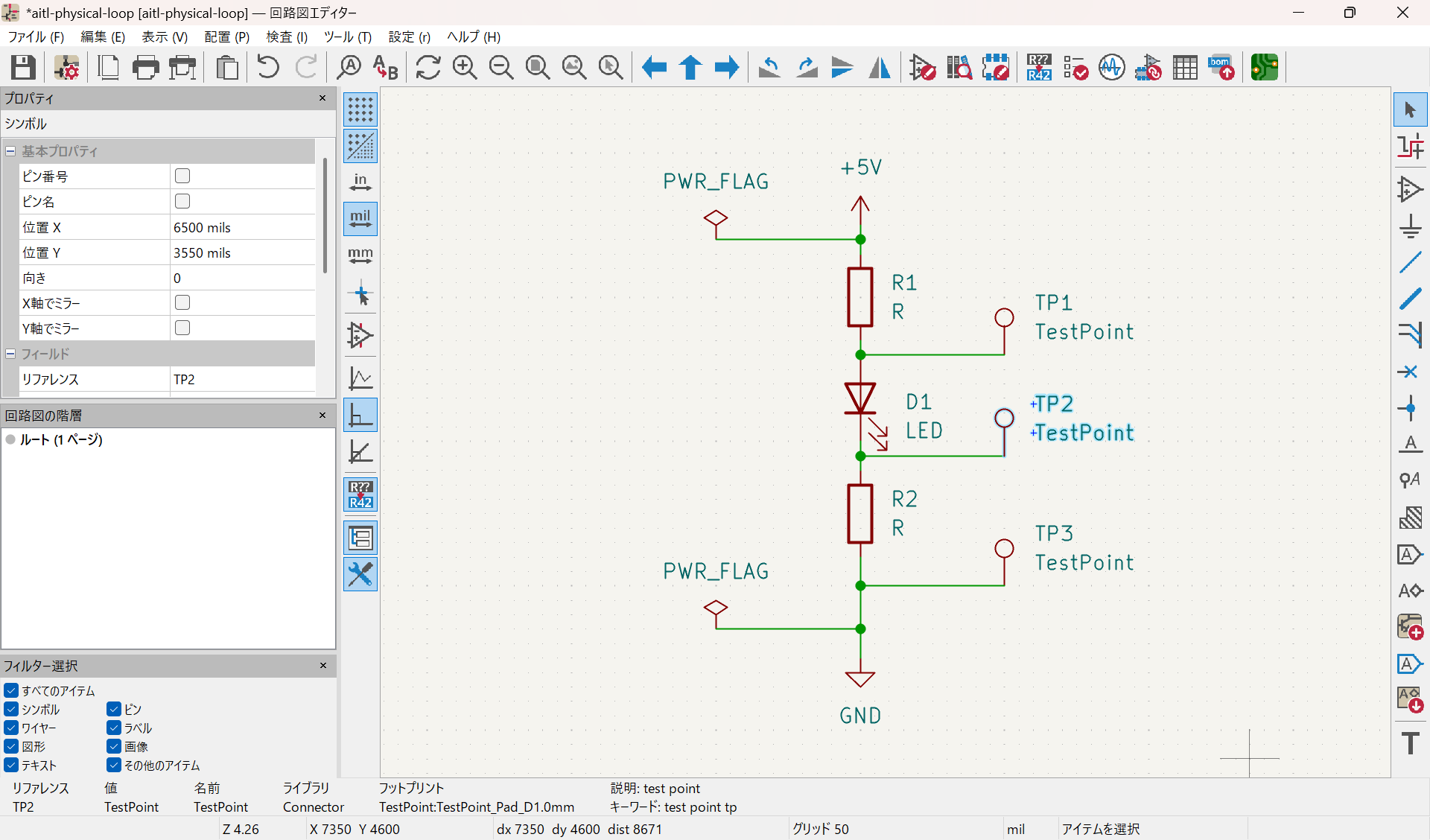

Fig.07 — v2 Schematic (Executable Physical Loop)

- 単一・閉じた V–I ループ

- 電流制限(R)と物理出力(LED)のみ

- 観測点(TP)は ループ非破壊

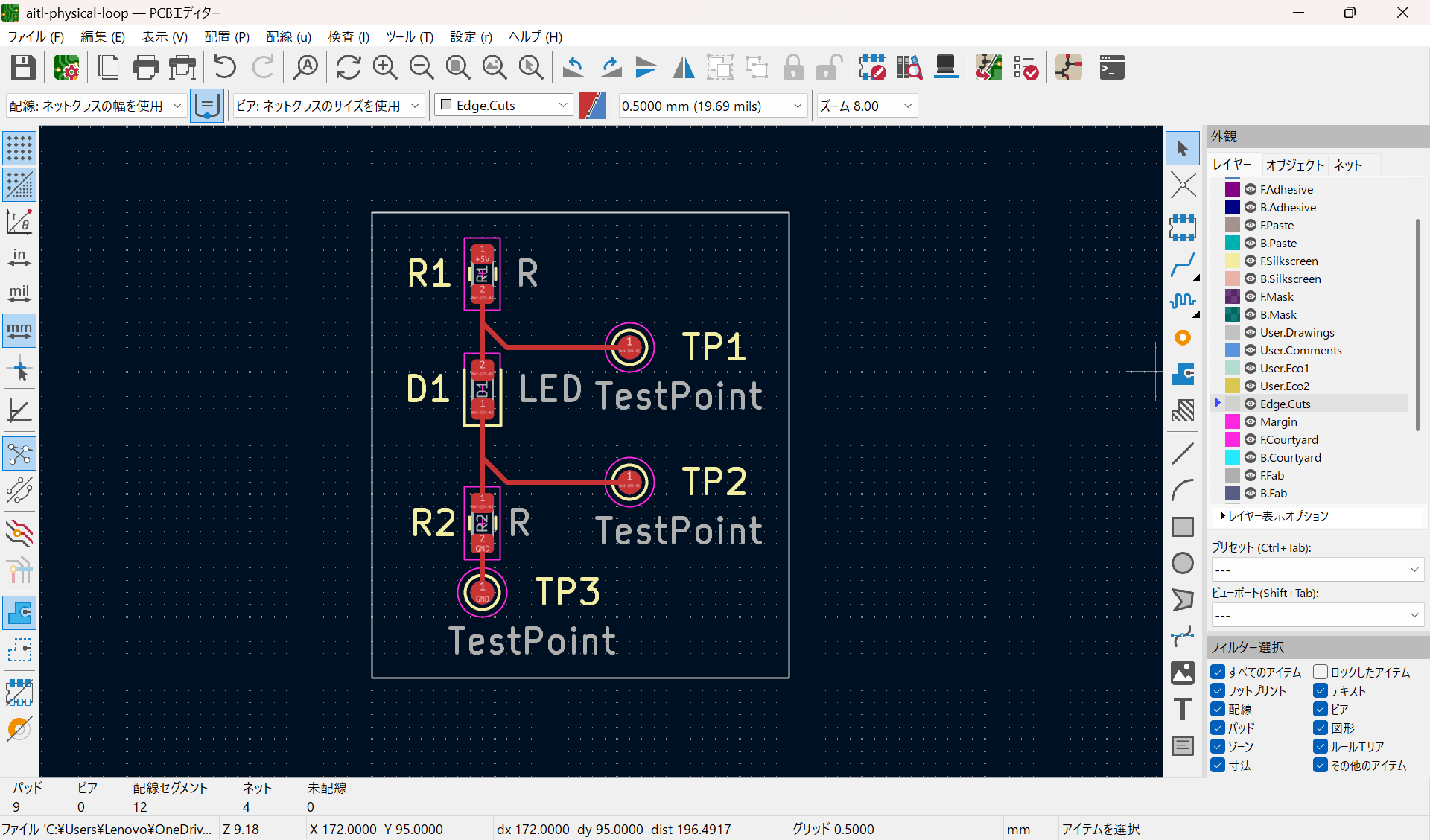

Fig.08 — v2 PCB Layout (DRC-clean, Manufacturable)

- Edge.Cuts 定義済み

- 未配線ゼロ/Zone の恣意性なし

- 物理制約がそのまま銅に反映

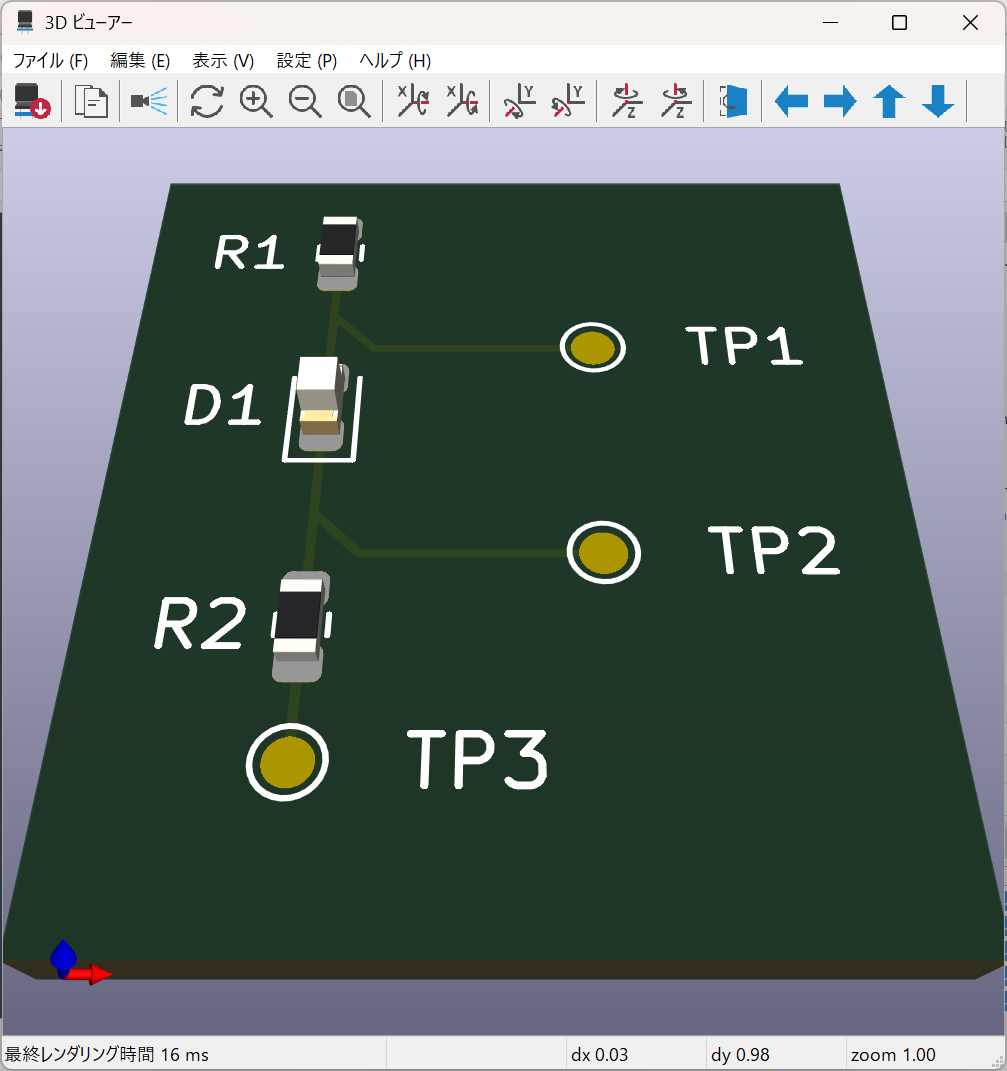

Fig.09 — v2 3D View (Embodied Reality)

- 実高さ・実クリアランス

- プローブ可視性を含む 実体としての境界

📏 v2 の設計原則(厳格)

v2 には できることより、できないこと が重要です。

含まれるもの(ONLY)

- 📐 明示的な Edge.Cuts(基板外形)

- 🔁 単一・閉じた電流ループ

- 🧮 電流制限要素(R)

- 💡 物理出力(LED)

- 📍 ループを破壊しない Test Point

含まれないもの(NEVER)

- ❌ MCU

- ❌ GPIO 意味論

- ❌ フィードバック

- ❌ タイミング

- ❌ 知能・判断

v2 は 制御の直前で止める ための版です。

🔄 物理ループとは何か

v2 が凍結するのは、次の 不可分な V–I ループ です。

VCC → R → LED → R → GND

これは論理構造ではありません。

物理事実です。

- どこで電圧が落ちるか

- どこで熱になるか

- どこを測ってもループが壊れないか

これらは 制御で決めてはいけない。

👁 観測可能性(Observability)

Test Point は次を満たします。

- ループを 切らない

- 電流経路を 変えない

- 測っても意味が 変質しない

「測れるが、触れない」

これが v2 の観測原則です。

🧱 AITL における v2 の位置づけ

| 層 | 役割 |

|---|---|

| LLM / AI | 意味・再設計 |

| FSM | 状態遷移 |

| PID | 連続制御 |

| v2 | 物理的な不変事実 |

| 物理 | 熱・光・電流 |

v2 は 最下層の凍結層。

🔒 安定性ルール(v2)

電流経路・V–I 意味・外形は変更不可。

変更が必要なら:

- v2.x:文書・図のみ

- v3:制御を含む新参照

🧾 まとめ

- v2 は便利にする版ではない

- v2 は制御を守る版である

- 制御の前に、銅を凍結せよ