【半導体:17】0.25µm DRAM Pause Refresh異常の物理的正体

topics: [“半導体”, “DRAM”, “故障解析”, “デバイス物理”, “プロセス”]

🧭 はじめに

前稿では、0.25µm世代DRAMにおいて

Pause Refresh 条件で観測された異常の「現象」のみを記録した。

本稿では、その現象が

どの物理挙動に対応していたのかを整理する。

結論から言えば、

これは単なる「保持不良」という言葉で括れる現象ではない。

支配因子は、セル容量でも回路でもなく、

プロセス起因のリーク物理だった。

🔍 観測結果が示していた物理的ヒント

前編で列挙した観測事実は、

すべて同じ方向を指していた。

- ランダム単一ビット

- 強い温度依存

- 一部可逆性

- 配置・データ非依存

これらを同時に満たす物理条件は限られている。

- 局所的に発生する

- 熱活性化される

- 永久破壊ではない

この時点で、

支配因子はほぼ一つに絞られていた。

🎯 支配因子:ジャンクションリーク

Pause Refresh 異常の正体は、

セルMOSトランジスタのジャンクションリーク電流である。

特に支配的だったのは、

- n⁺ / p⁻ 接合近傍

- 拡散端部

- 絶縁境界(STI / LOCOS)周辺

に存在する 欠陥準位を介したリークだった。

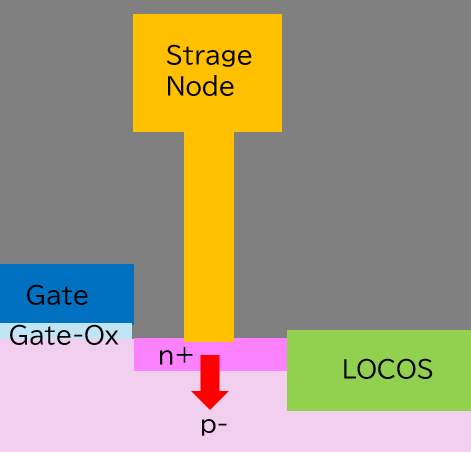

🧬 リークが発生する断面構造(参照図)

ここで、Pause Refresh 異常を理解するための

物理的前提となる断面図を示す。

図1:0.25µm DRAMセルにおける ジャンクション端部リーク経路(概念断面図)

この図が示すのは、

リークが「セル全体」ではなく、

ごく局所的な構造端部に集中するという事実である。

- ゲート端

- 拡散端

- 絶縁端

これらはすべて、

プロセスダメージが蓄積しやすい場所でもある。

🔁 SRH再結合が作る振る舞い

このリークは、

Shockley–Read–Hall(SRH)再結合に支配されていた。

SRHリークの特徴は明確だ。

- 温度に対して 指数関数的に増加

- 欠陥密度に強く依存

- デバイス寸法より プロセス履歴に敏感

この特性により、

- 高温で突然 Fail が増える

- 温度を下げると Fail が消える

という 可逆的挙動が自然に説明できる。

🎲 なぜ「ランダム単一ビット」になるのか

SRHリークは、

- ウェーハ全面に均一

- セルごとに同一

ではない。

欠陥は、

- 局所的

- 統計的

- 再現性はあるが配置規則を持たない

という性質を持つ。

その結果、

- 連続ビットにならない

- 行・列依存を持たない

- 空間的な“地図”が描けない

ランダム単一ビット Failとして観測された。

🚫 セル容量は関係していなかった

ここが重要な転換点である。

Pause Refresh 異常は、

- キャパシタ容量不足

- 設計マージン不足

では説明できなかった。

容量を増やしても、

- 高温条件では Fail は消えない

- Fail 発生セルは固定

だったからだ。

保持時間は、

容量ではなくリークで決まっていた。

🧪 プロセス履歴との強い相関

Fail発生率は、

特定のプロセス条件と強く相関していた。

代表例は次の通り。

- プラズマエッチング条件

- ドライアッシング工程

- 接合形成後の表面処理

これらはいずれも、

界面欠陥密度を増やす方向

に働く。

プロセス条件を変えると Fail が減り、

元に戻すと再発する。

この再現性は、

物理起因であることの決定的証拠だった。

⏸ なぜ Pause 条件でだけ顕在化したのか

通常動作や通常リフレッシュ中は、

- 書き込み

- 読み出し

- 定期的な再充電

によって、リークは“見えにくい”。

Pause Refresh 条件では、

- 電荷は一切補充されない

- 時間だけが経過する

このため、

リーク電流 × 無補充時間

が、そのままデータ消失として現れる。

Pause Refresh は、

リーク物理をそのまま露出させる条件だった。

🧾 まとめ(物理編)

0.25µm DRAM の Pause Refresh 異常は、

- 設計の問題ではない

- 容量の問題でもない

プロセス起因の欠陥が作るリーク物理だった。

- 支配因子:SRHリーク

- 感度因子:欠陥密度

- 増幅因子:温度

- 顕在化条件:Pause(無補充時間)

この現象は、

設計で議論すべき対象では最初からなかった。

🔗 一次情報(参照元)

-

Legacy Technology Archive

https://samizo-aitl.github.io/Edusemi-Plus/archive/legacy/ -

0.25µm DRAM ケース

https://samizo-aitl.github.io/Edusemi-Plus/archive/legacy/dram_025um/ -

Pause Refresh Fail 詳細

https://samizo-aitl.github.io/Edusemi-Plus/archive/legacy/dram_025um/pause/

⏭ 次回予告

次稿から、

PSRAM(2001年)ケースに入る。

まずは

「PSRAMは何を狙った技術だったのか」

――構造と前提だけを扱う。