【半導体:16】0.25µm DRAMで観測されたPause Refresh異常

topics: [“半導体”, “DRAM”, “故障解析”, “信頼性”, “プロセス”]

🧭 はじめに ― 理屈が追いつかない異常

0.25µm世代のDRAMでは、

従来の経験則では説明できない異常が観測された。

それが Pause Refresh Fail である。

本稿では、

- どのような条件で

- どのような挙動として

- どのように観測されたのか

を 解釈を加えずに 記録する。

原因や物理的説明は 次稿 に回す。

ここでは、あくまで「現象そのもの」に限定する。

🧪 Pause Refresh テストとは何か

Pause Refresh テストは、

DRAMセルの 保持特性だけ を切り出して評価する試験である。

基本的な手順は以下の通り。

- 📝 セルに既知データを書き込む

- ⏸ リフレッシュ動作を停止する

- ⏳ 一定時間、完全に放置する

- 🔍 再度読み出し、ビットエラーを取得する

アクセスもリフレッシュも行わない状態で、

どのセルが、どれだけ電荷を保持できるか を観測する。

当時としては、

特殊な評価ではなく 標準的な信頼性評価項目の一つだった。

🔍 観測された異常

① Fail bit map が「描けない」

最初に強い違和感が出たのは、

Fail bit map の分布だった。

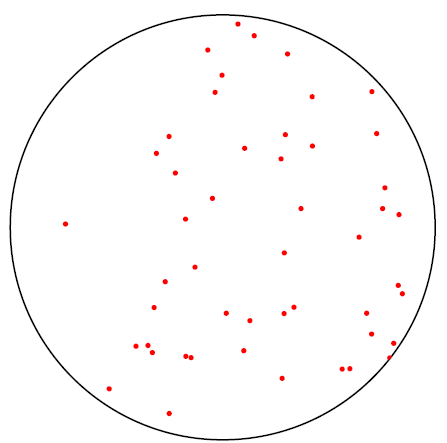

図1:Pause Refresh 条件下で取得した Fail bit map (0.25µm 世代 DRAM)

観測された特徴は以下の通り。

- 行方向の偏りがない

- 列方向の偏りがない

- ブロック単位の集中もない

Failは、

ランダムに点在する単発ビットとして現れた。

特定ワードライン、特定領域、

特定配線方向に 地図が描けない。

これは、

従来のレイアウト起因不良や配線起因不良とは

明確に様相が異なっていた。

② 単一ビット支配

Pause Refresh Fail の大半は、

- 連続ビットではない

- クラスタ化しない

単一ビットエラーとして観測された。

複数ビット同時崩壊や、

面積に比例した壊れ方は見られない。

セル単位で、

孤立して壊れているように見える挙動だった。

③ 温度依存が極端

温度条件を変えると、

Fail数は 非線形に変化した。

- 🌡 室温付近:Failはほぼ観測されない

- 🔥 高温条件:Failが急激に増加する

一方で、温度を下げると

Failが消失するセルも存在した。

この 可逆性 は、

永久欠陥や機械的破壊とは異なる特徴だった。

④ データパターン依存がない

書き込みデータを変えても、

- All-0

- All-1

- チェッカ

- ランダム

Failの分布や数に有意な差は現れない。

データ内容や隣接ビット状態による

再現性の変化は確認されなかった。

🧱 セル構造との対応を考えるための前提図

この時点では 原因は未確定 だったが、

議論の前提として

セル構造の空間関係は共有されていた。

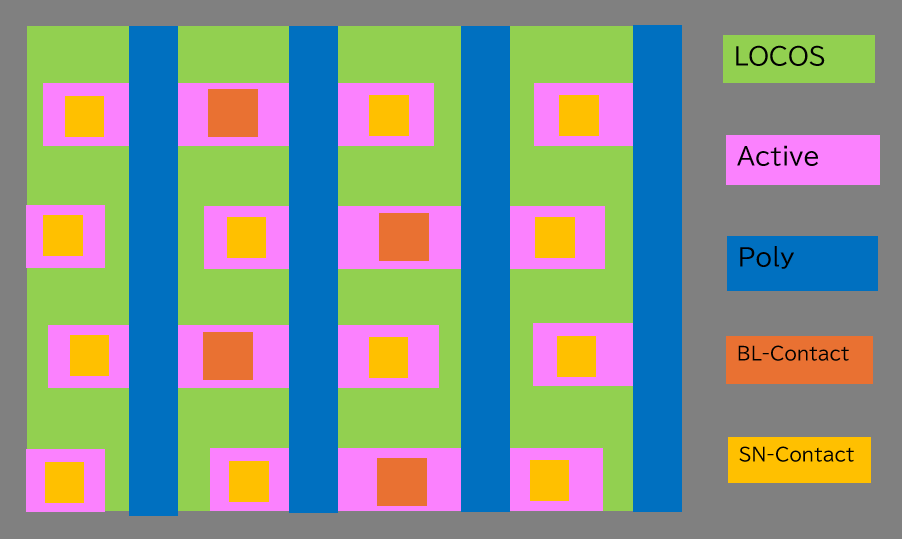

メモリセル平面レイアウト(参照)

図2:DRAMメモリセル平面レイアウト(概念図)

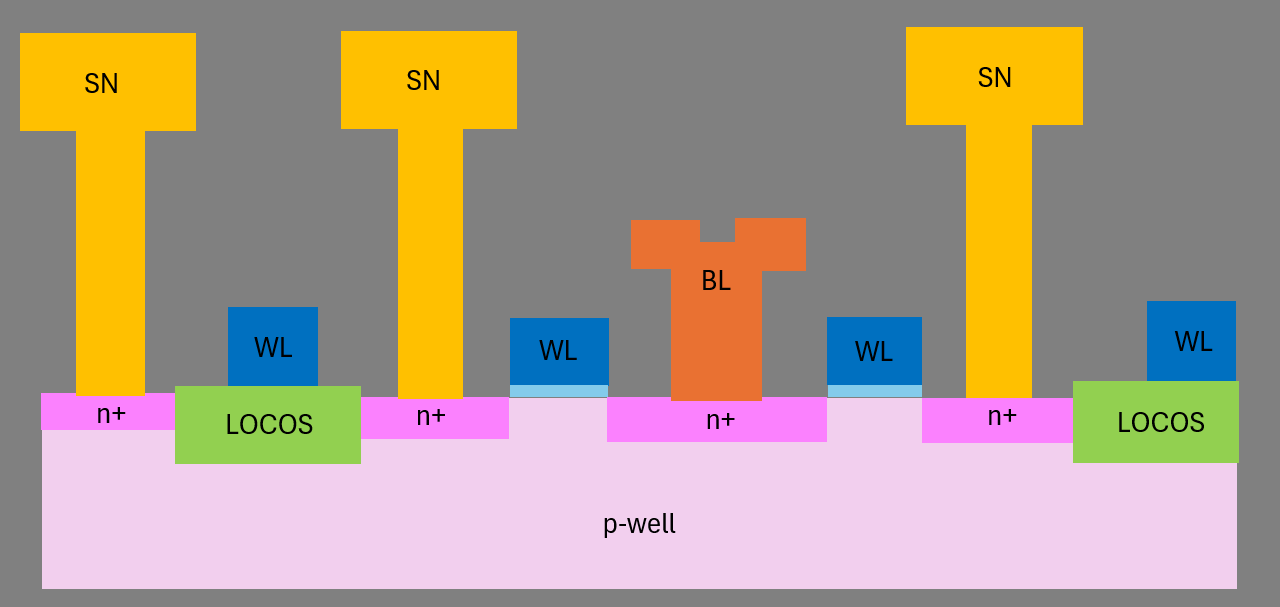

メモリセル断面構造(参照)

図3:DRAMメモリセル断面構造(概念図)

重要なのは、

これらの図から 直接原因を読み取れなかった という点である。

- 特定構造に紐づかない

- 特定方向性を示さない

- 配置依存性が見えない

Fail bit map のランダム性は、

セル構造と1対1に対応しなかった。

✅ この時点で確定していた事実

観測結果から、

次の点だけは比較的早い段階で共有されていた。

- セル容量不足を示す兆候ではない

- レイアウトや配線起因の不良ではない

- アクセス動作中に発生する故障ではない

Pause Refresh Fail は、

保持中に、ランダムなセルで電荷が失われる

という現象としてのみ、

確実に存在していた。

⚠️ 「おかしさ」が示していたもの

この異常は、

- 再現性はある

- 条件(特に温度)に強く依存する

- しかし空間的な規則性がない

という特徴を同時に持っていた。

この段階では、

- 故障名を与えること

- 原因を仮定すること

のどちらも まだ適切ではなかった。

分かっていたのは、

従来のDRAM不良像とは一致しない

という事実だけである。

🧾 まとめ(現象編)

0.25µm DRAMで観測された Pause Refresh 異常は、

次の特徴を持っていた。

- Pause Refresh 条件でのみ顕在化

- Failはランダムな単一ビット

- 強い温度依存と一部可逆性

- データ・配置依存性なし

違和感だけが、先に存在していた。

この違和感が、

後にまったく別の物理領域へ

議論を押し出すことになる。

🔗 一次情報(参照元)

-

Legacy Technology Archive

https://samizo-aitl.github.io/Edusemi-Plus/archive/legacy/ -

0.25µm DRAM ケース

https://samizo-aitl.github.io/Edusemi-Plus/archive/legacy/dram_025um/ -

Pause Refresh Fail 詳細

https://samizo-aitl.github.io/Edusemi-Plus/archive/legacy/dram_025um/pause/

⏭ 次回予告

次稿では、

この現象が どの物理挙動に対応していたのか を扱う。

解釈はするが、

設計の話には踏み込まない。