【半導体】⚡ 08-09. HCIとは何か ― 高電界がMOSFETを壊す理由

topics: [“半導体”, “HCI”, “信頼性”, “MOSFET”, “BSIM4”]

⚡ はじめに

前回の記事では、

NBTI(Negative Bias Temperature Instability) という

「時間と温度」に支配される信頼性劣化を扱いました。

本記事では、もう一つの代表的な劣化機構である

👉 HCI(Hot Carrier Injection)

を取り上げます。

- NBTI:⏱️ 時間 × 温度

- HCI:⚡ 電界 × エネルギー

つまり HCI は、

「速く・強く動かそうとした代償」

として現れる劣化現象です。

🔥 HCIとは何か

HCI は MOSFET において、

- 高いドレイン電圧

- ドレイン近傍の強電界

- 高エネルギーキャリア(Hot Carrier)

が発生したときに起こる

信頼性劣化現象 です。

特徴として:

- 主に nMOSFET で顕在化しやすい

- 高速動作・高電圧条件で加速される

という点が、NBTI との大きな違いです。

🧠 何が起きているのか(物理像)

ドレイン近傍では、

- 急峻な電位勾配

- 非常に強い横電界

が発生します。

その結果:

- キャリアが強く加速される

- 高エネルギー状態(Hot Carrier)になる

- 一部がゲート酸化膜中に注入される

- 界面準位・トラップが生成される

👉 MOSFET 自身が、自分の酸化膜を傷つける

これが HCI の本質です。

📉 デバイス特性への影響

HCI による損傷は、以下の形で現れます。

- しきい値電圧の変動

- キャリア移動度の低下

- ドレイン電流の低下

- 出力特性(Vd–Id)の劣化

特に重要なのは:

高 $(V_d$) 動作を続けた「後」の DC 特性変化

として観測される点です。

NBTIとの違い 🆚

| 観点 | NBTI | HCI |

|---|---|---|

| 主対象 | pMOS | nMOS |

| 支配要因 | 温度・時間 | 電界・電圧 |

| 劣化箇所 | 界面準位 | 界面+酸化膜 |

| 主な影響 | (V_t) シフト | μ低下・(I_d)低下 |

| 依存性 | 時間依存 | 電圧・電界依存 |

👉 両者は完全に別の劣化機構

👉 対策も設計指針も異なります。

📐 BSIM4におけるHCIの扱い

BSIM4 では HCI を、

- 劣化を モデルパラメータ変化 として表現

- 電界・電圧条件に依存した劣化量を仮定

- 劣化前後の特性差を比較

という形で扱います。

ただし重要な点として:

BSIM4 単体では「時間発展」を直接解かない

そこで SemiDevKit では、

- 🧪 SPICE:t = 0 の正確な特性取得

- 🧮 Python:t > 0 の劣化モデル適用

という ハイブリッド信頼性解析 を採用しています。

🧰 SemiDevKitによるHCI解析

使用するモジュール:

- BSIM4 Analyzer Reliability

https://samizo-aitl.github.io/SemiDevKit/bsim/bsim4_analyzer_reliability/

このフレームワークでは:

- 初期 Vg–Id / Vd–Id 特性取得

- gmmax 法・定電流法による Vth 抽出

- HCI 劣化モデルの適用

- 劣化後特性の再構築

を 完全自動 で行います。

🔬 HCI解析フロー

t = 0

├─ VG–ID sweep

│ ├→ Vtg0(gmmax 法)

│ └→ Vtc0(定電流法)

├─ DC 抽出

│ └→ Idlin0 / Idsat0

t > 0

├─ ΔVth(t) モデル適用

├─ ΔId(t) モデル適用

├─ Vtg1 / Vtc1 / Idlin1 / Idsat1 再構築

→ CSV 出力

→ 劣化プロット生成

→ Vg–Id 重ね描き

🚀 実行例

cd bsim/bsim4_analyzer_reliability/run

python run_hci_nmos.py

📊 解析結果例

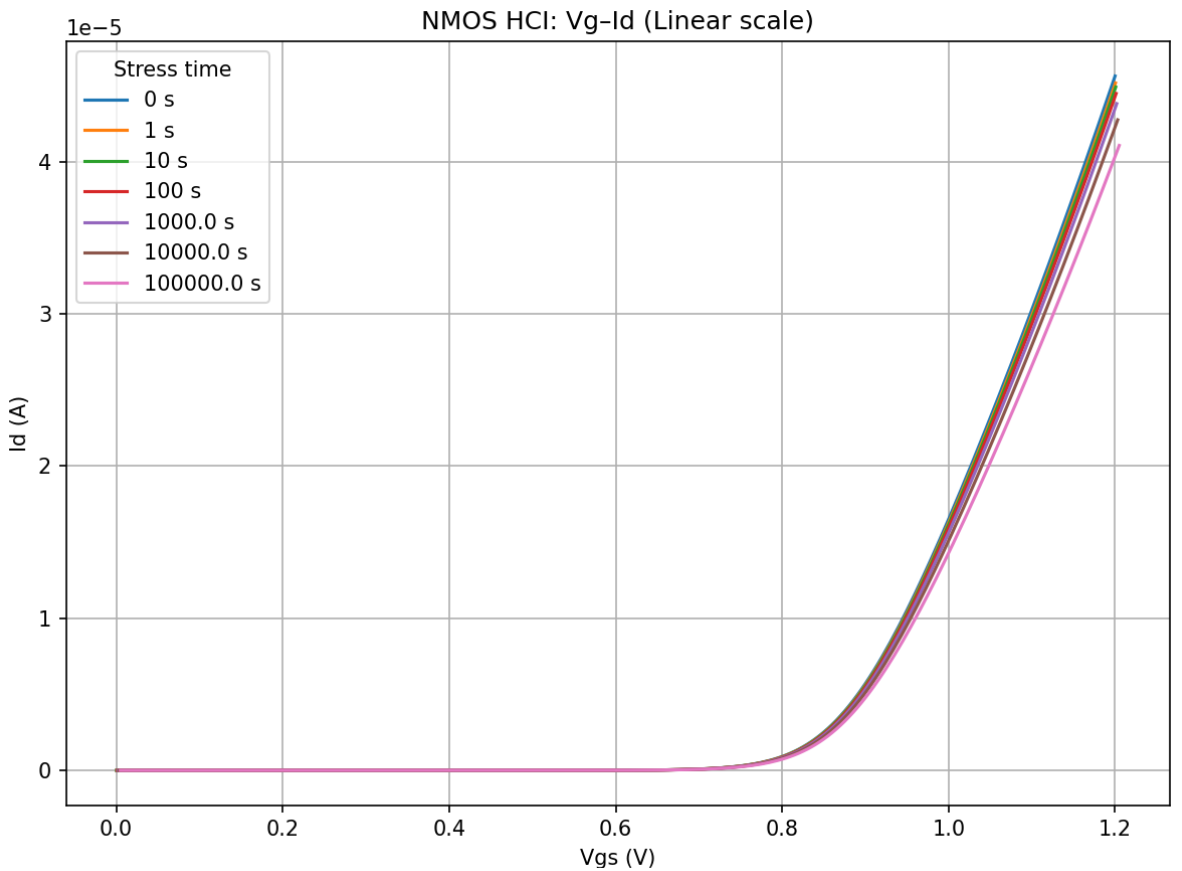

■ NMOS HCI:Vg–Id 劣化(Linear)

👉 gm 低下・オン電流減少

👉 高速パスの遅延要因になる

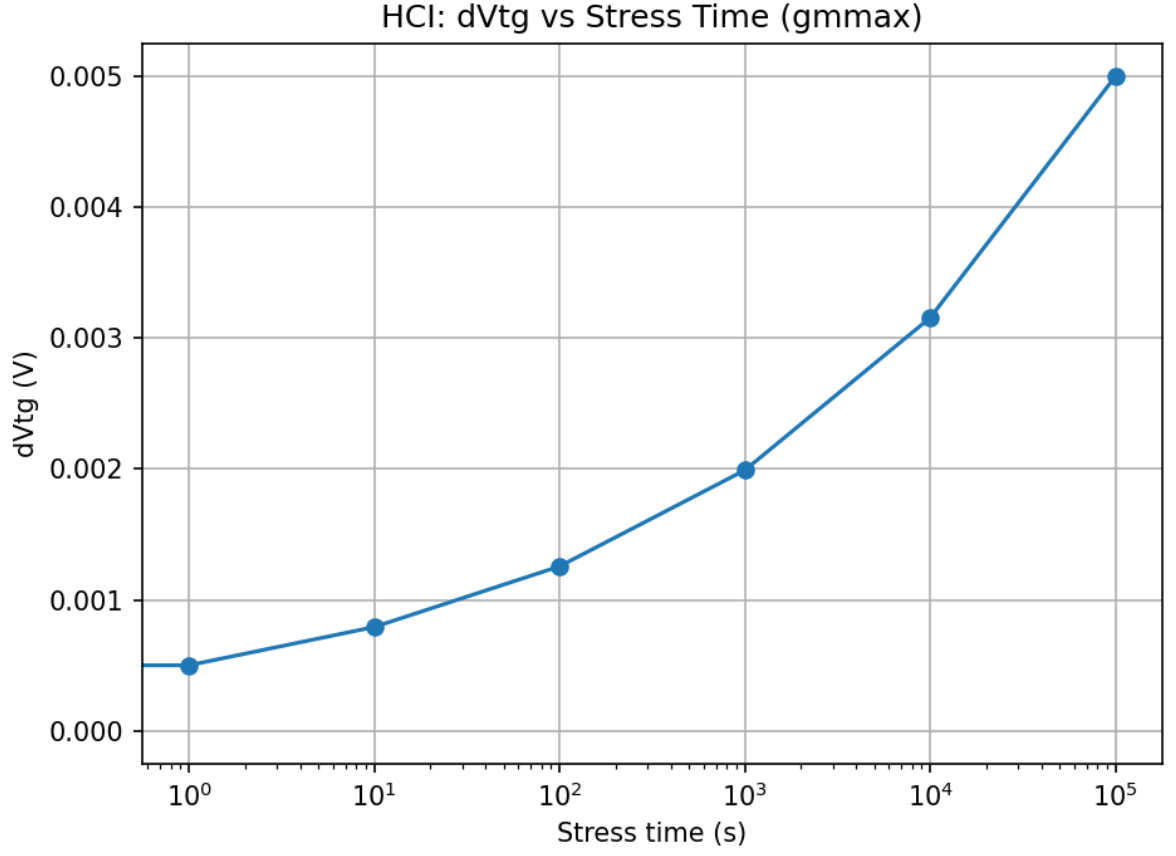

■ NMOS HCI:ΔVtg vs Stress Time

👉 初期劣化が支配的

👉 高電圧条件ほど劣化が急

⚠️ なぜHCIが重要なのか

HCI は特に:

- 高速クロック設計

- 高電圧マージン設計

- 出力ドライバ

と強く結びついています。

「速さを取りに行くと、寿命を削る」

というトレードオフを、

HCI は最も分かりやすく示します。

🔗 TCAD / BSIM / SPICE の一本線

HCI も、これまでと同じ流れの上にあります。

- TCAD:ドレイン近傍の高電界・高エネルギー

- BSIM4:劣化をパラメータ化

- SPICE:回路特性への影響を評価

👉 物理 → モデル → 回路 → 劣化

この一本線が、

HCI 編で完全に閉じます。

📚 シリーズ総まとめ

本シリーズでは、以下を一貫して追ってきました。

- TCAD(物理現象)

- BSIM4(コンパクトモデル)

- Paramus(モデル生成)

- SPICE(DC / AC / CV)

- DIM(L/W スケーリング)

- 信頼性(NBTI / HCI)

SemiDevKit を使えば、

商用EDAに依存せず、この全工程を体験できます。

📝 まとめ

- ⚡ HCI は高電界起因の信頼性劣化

- 🔵 主に nMOSFET で顕在化

- 🚀 高速・高電圧設計とトレードオフ

- 🧪 BSIM4 + SPICE + Python で影響を評価可能

MOSFET は、

「速く動くか」ではなく

「速く動き続けられるか」

で評価される時代です。

🔗 関連リンク

- SemiDevKit(全体)

https://samizo-aitl.github.io/SemiDevKit/