🎓 Samizo-AITL Portal

半導体・MEMS・制御・AIの設計資料集

物理モデル/PID・FSM による実時間制御/RTL→GDS 実装/PoC を公開

🚀 このポータルで得られること

Samizo-AITL は、

半導体・MEMS・制御・AI に関する設計資料を、

物理モデルと実装結果に基づいて公開している技術アーカイブです。

提供内容

- 物理モデルおよびデバイス前提を明示した設計資料

- PID/FSM を中心とした実時間制御アーキテクチャ例

- NN/RL/LLM を「制御を置き換えない」前提で用いた設計支援例

- RTL→GDS、OpenLane、SPICE、PoC の再現可能な実装

🎯 対象読者

- 半導体/MEMS/制御系の設計・検証に関わる技術者

- PID・FSM を用いた実時間制御を扱う設計者

- AI を制御ループに直接組み込まない設計方針を検討している人

※ 入門者向けの解説サイトではありません

🗺️ AITL Structure Map(全体構造)

flowchart TB

%% ===== Physical Layer =====

subgraph PL["Physical Layer"]

P["Physical / Devices / MEMS"]

end

%% ===== Control Layer =====

subgraph CL["Control Layer"]

M["Models"]

C["Control Theory"]

R["Real-time PID"]

end

%% ===== Supervisory & Design Layer =====

subgraph SL["Supervisory & Design Layer"]

S["FSM Supervisor"]

A["Adaptive Assist (NN / RL, bounded)"]

I["LLM (Design-time only)"]

end

%% ===== Flow =====

P --> M --> C --> R --> S

S --> A

S --> I

%% ===== Style =====

style PL fill:#e6f2ff,stroke:#1f4ed8,stroke-width:2px

style CL fill:#e9ffe6,stroke:#1f8b24,stroke-width:2px

style SL fill:#fff3e6,stroke:#d86b1f,stroke-width:2px

style I stroke-dasharray:5 5

以下に、各レイヤの役割を示します。

-

Physical Layer

物理・デバイス・MEMS により、

システムの制約条件、動作限界、不確実性を定義します。 -

Control Layer

物理モデルに基づく制御理論(PID)により、

安定性、応答特性、性能を規定します。 -

Supervisory & Design Layer

- FSM:状態判定、状態遷移、介入可否の管理

- NN / RL:FSM が許可した範囲での実時間適応補助(bounded)

- LLM:非実時間での解析、再設計、設計支援

※ LLM は設計時(非実時間)のみで使用し、

実時間制御ループには介入しません。

🗂 Samizo-AITL Directory Overview(全体像)

このディレクトリ構成そのものが、設計思想です。

Samizo-AITL/

├─ 01_DevEnv/ 環境・再現性(VSCode / Python / Toolchain)

│

├─ 02_CodeGen/ 実装・制御・生成

│ ├─ PID 実時間制御(安定性・V–I 制御)

│ ├─ FSM 監督・状態遷移・モード管理

│ ├─ NN_RL 制限付き実時間適応補助(FSM許可下)

│ └─ LLM 設計監督・再設計支援(非実時間)

│

├─ 03_Docs/ 理解・教育・設計思想

│ ├─ Edusemi-v4x

│ ├─ EduController

│ └─ Edusemi-Plus

│

└─ 04_Archives/ PoC・履歴・技術資産

🗺 このポータルの歩き方

-

設計アーキテクチャ

物理モデルを前提とした AITL 構成と各レイヤの役割 -

物理・デバイス

半導体物理、デバイス構造、MEMS、物理的制約条件 -

制御アーキテクチャ

モデルに基づく実時間制御(PID)と FSM による状態監督 -

知能(設計時)

FSM 監督下での設計時解析および LLM による非実時間支援 -

PoC 実装

実動作システムによる検証例

📝 Essays / Design Notes(Zenn / Qiita)

🧠 設計方針、物理前提、AITL 構造に関する記事は、

GitHub 上の Markdown 原稿を一次情報(正本)として管理しています。

📚 Zenn / Qiita は公開用チャネルであり、

Single Source of Truth は GitHub Pages です。

📚 Zenn(構造・アーキテクチャ整理)

🏛 設計アーキテクチャおよび構成整理

🏛 物理モデルを前提とした設計視点の整理

🏛 AITL(PID × FSM × LLM)の責務分離設計

📜 Qiita(導入・補足・実装例)

🔧 導入向け解説

🔧 実装補足および PoC 説明

🔧 単体トピックの切り出し記事

1️⃣ 📘 Edusemi-v4x

半導体プロセス・デバイス・回路設計を、物理起点で体系化する基幹教材。

- 電子物性・プロセス条件・デバイス構造の因果関係を整理

- 回路特性を「結果」ではなく「物理の帰結」として理解

- 教科書断片ではなく、設計につながる物理体系を構築

👉 Samizo-AITL 全体の物理基盤となる中核教材。

🔹 特別章:SystemDK(System Design Kit)

物理・デバイス・回路を前提として、

SI / PI / 熱 / 応力 / EMI を含む「実装・統合設計」へ展開する特別章。

- デバイス単体では終わらない「システム制約」を物理から整理

- SoC / Chiplet / Package / Board を貫く設計視点

- 教材でありつつ、実設計の思考フレームとしても利用可能

👉 Edusemi-v4x における「物理 → システム統合」への橋渡し位置づけ。

🧩 OpenLane Guide

本教材では OpenLane を RTL → GDS を確認するための実装手段として使用しています。

OpenLane の 環境構築・安定運用・再現性確保(WSL2 / Docker / PDK / OpenLane1・2の分離 / rollback・export戦略) については、以下の専用ガイドに分離しています。

2️⃣ 📐 SemiDevKit

物理モデルから SPICE・信頼性・レイアウトまでを接続する実装キット。

- 物理モデルを SPICE モデルへ落とし込む

- 信頼性・ばらつき・設計マージンを考慮

- デバイス理解を 設計フローとして実装する

👉 物理理解を「設計作業」に変換するための橋渡し。

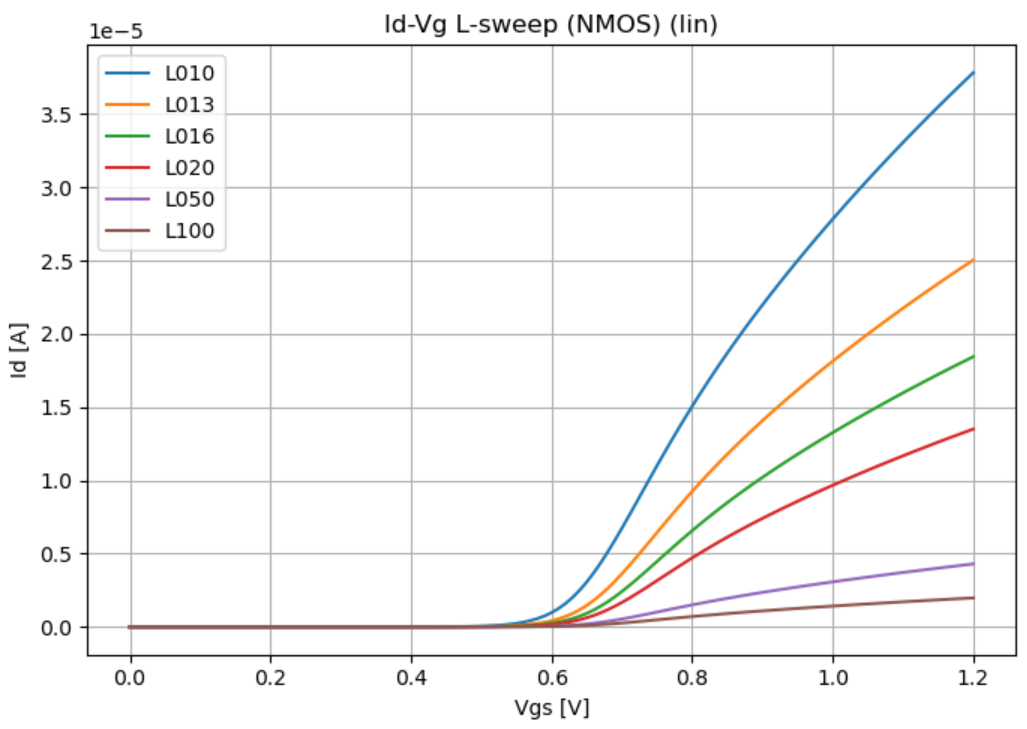

■ Device Modeling Example(SCE対応)

BSIM4モデルによるNMOS Vg–Id特性(Linear領域)。

チャネル長Lの短縮に伴うId増大と勾配変化を通じて、

Short Channel Effect(Vth roll-off / mobility degradation)を反映したデバイス挙動を可視化。

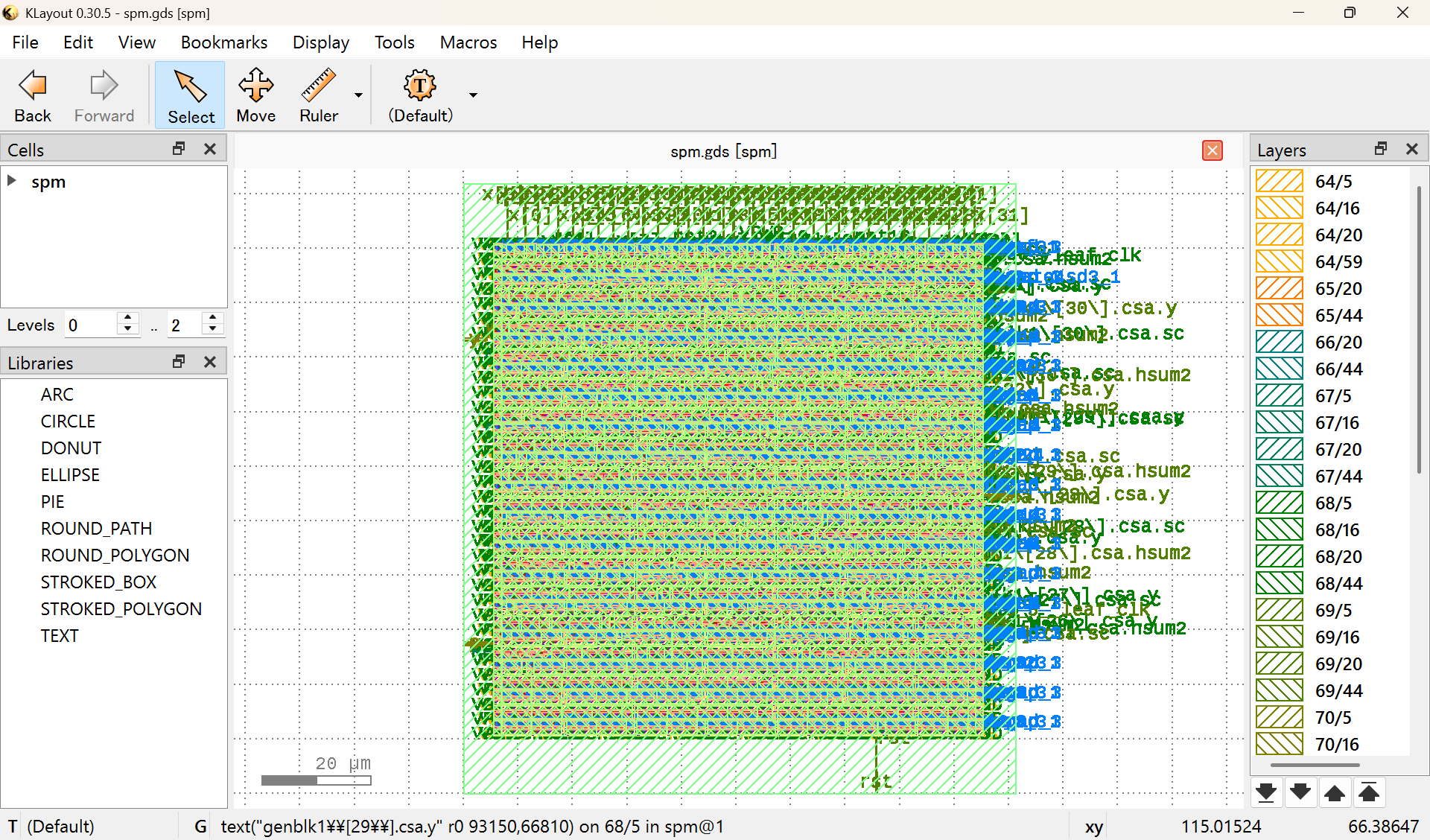

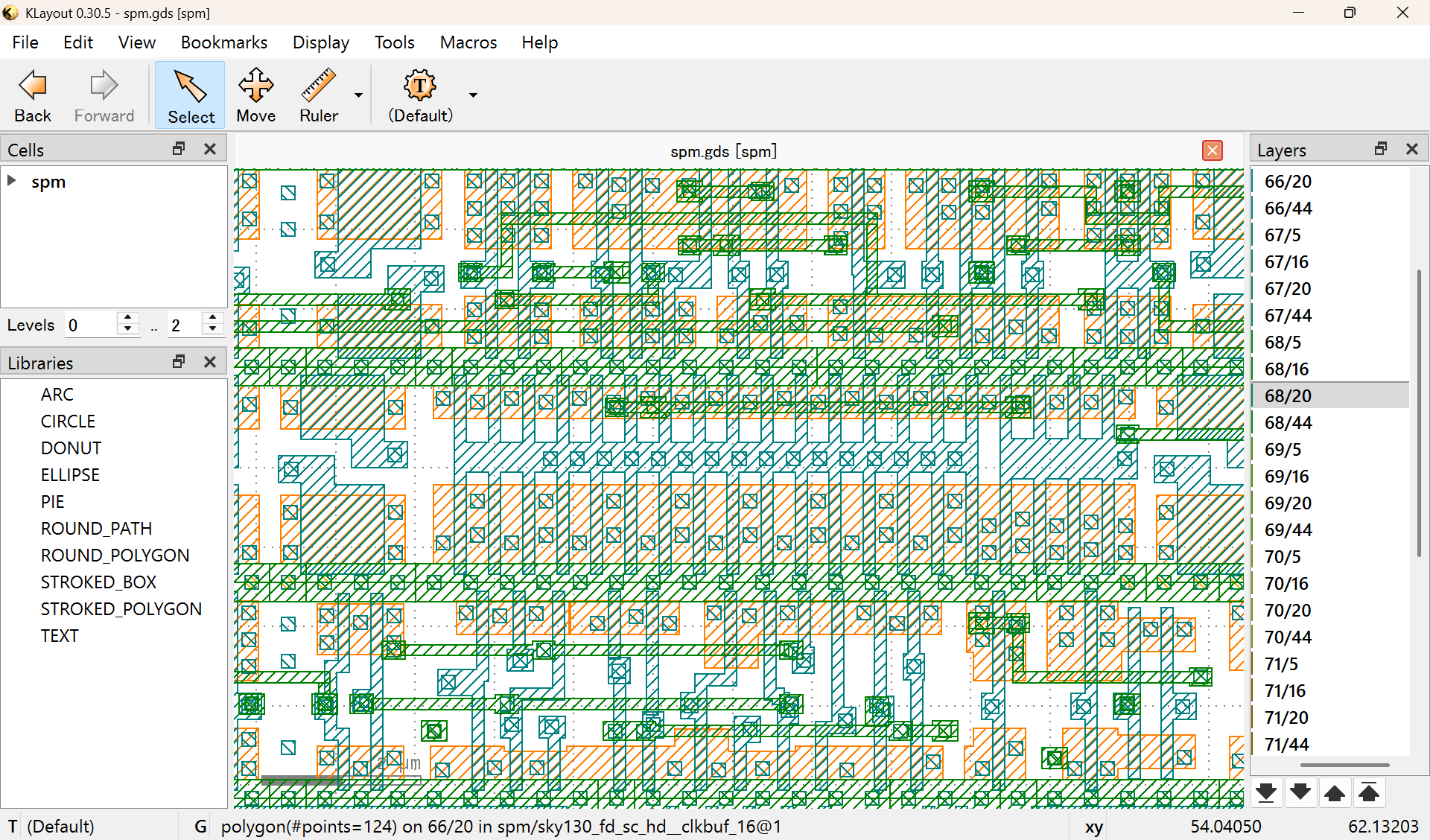

🧱 openlane2-sram|SRAMマクロ統合・物理設計実証

OpenLane2(v2)を用いて SRAM hard macro を統合し、RTL → GDS まで完走する

マクロ対応・物理設計の実践教材。

- SRAM を external hard macro(blackbox / LEF / GDS) として扱う

- FIXED 配置・halo / keepout を含む macro-aware floorplanning

- OpenLane2 Classic flow による 最終 GDS 生成

- SoC 物理設計で一般的な 「SRAM 中身は見ない」設計作法を明示

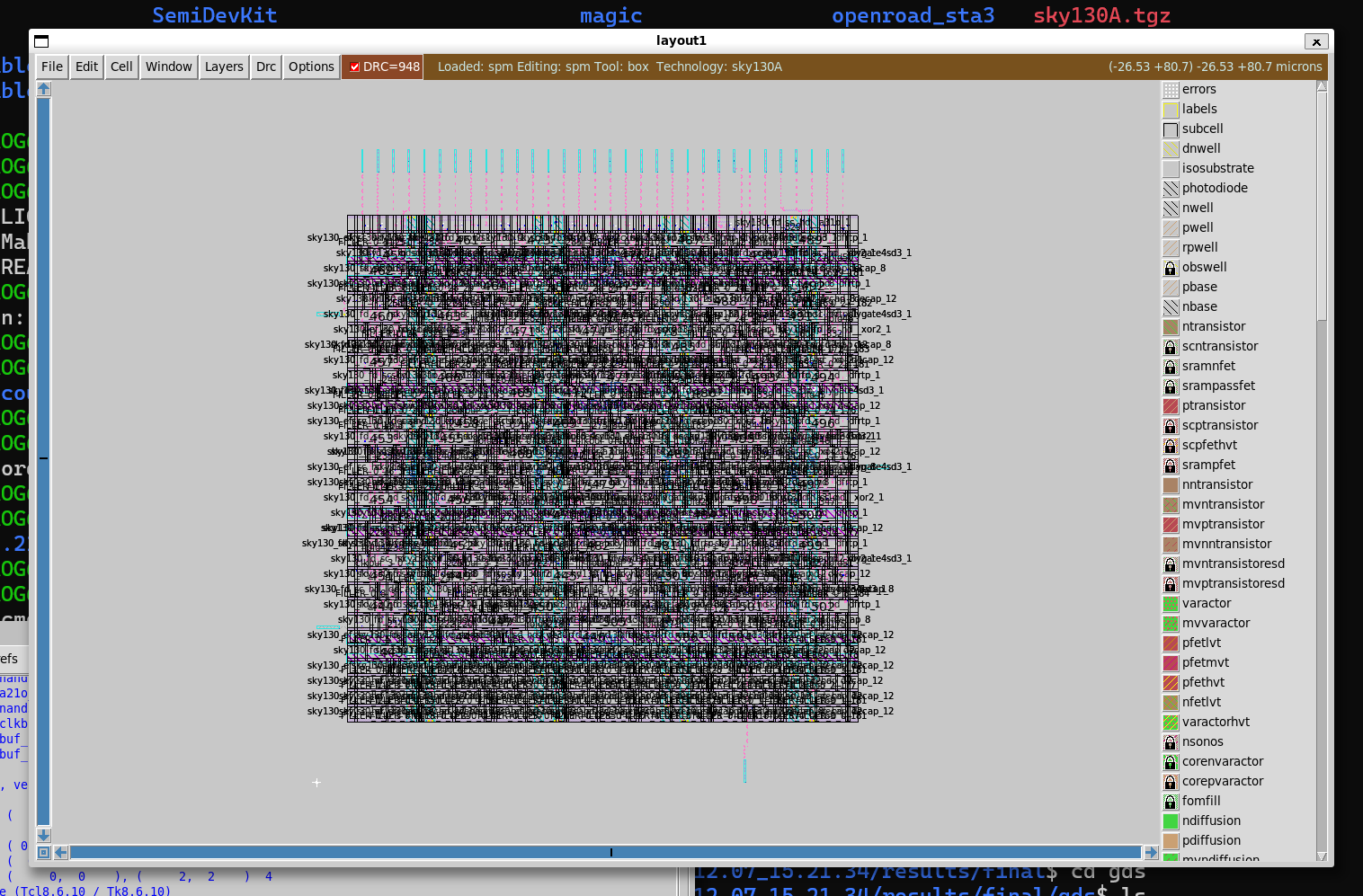

🔎 レイアウト検証(GDS)

図1:SRAM マクロのブロックレベル表示

図2:SRAM マクロ周辺のスタンダードセルレベル表示

注記:本 SRAM は、抽象ビュー(LEF / GDS)を用いた 固定ハードマクロ として統合されています。

内部のトランジスタレベルのレイアウトは意図的に可視化されておらず、これは SoC の物理設計における標準的な実務慣行と一致しています。

3️⃣ 📘 Edusemi-Plus

材料・装置・産業構造を、物理視点で拡張する補助教材。

- 製造装置・材料技術と物理原理の関係整理

- 半導体産業構造・技術選択の背景を理解

- Edusemi-v4x の物理体系を 現実世界へ拡張

👉 「なぜこの技術が選ばれているか」を理解するための補助教材。

🕰 Legacy Technology(Failure & Recovery Archive)

Legacy Technology は、過去技術の回顧ではありません。

物理・プロセス・使用条件が どのように失敗を生み、

それが歩留まり・製品戦略・撤退判断にどう接続されたかを記録した

因果構造ベースのケーススタディ集です。

- 失敗は「結果」ではなく 設計制約の可視化

- 成功は「最適解」ではなく 制約下での回復

- 多くの構造は、現代の SoC / AI / 先端デバイスでも再出現します

👉 「なぜ AI や制御は現実を無視できないのか」を、

実在した 製造・テスト・市場判断の連鎖から理解するための資料群です。

▶ 主なケース

-

0.25µm DRAM (1998)

プロセス統合・リーク支配・Pause / Disturb 不良・Bin戦略

→ 歩留まり回復と限界の顕在化

🔗 Open DRAM 0.25µm Case -

PSRAM (Pseudo-SRAM, 2001)

DRAM派生アーキテクチャをモバイル条件(90 °C)で運用した境界事例

→ 技術的成功と戦略的撤退

🔗 Open PSRAM Case

🔐 機密性に関する明示

本アーカイブは、20年以上前(1990年代後半〜2000年代初頭)の

半導体技術を対象としています。現行製造に適用可能な プロセスレシピ、設計ルール、装置調整条件などの

企業機密は一切含まれていません。

本資料は 失敗・回復・意思決定の因果構造を保存することを目的としています。

🎛 Control & Supervisory Architecture

実時間制御(PID)を中核とし、FSM による状態監督と非実時間知能によって設計責務を分離する制御アーキテクチャ

4️⃣ 📘 EduController

PID・FSM を中心に、制御系の構造そのものを理解するための教材。

- PID による実時間制御と安定化の役割

- FSM による状態監督・モード遷移の意味

- 「制御ロジック」と「制御構造」の違いを明確化

👉 制御を“組む前に考える”ための基礎教材。

▶ Control Playground(Time Response Demo)

固定 PID 制御器が、

色付きかつ状態依存の外乱にさらされたときの時間応答を可視化したデモです。

- スライダーなし

- チューニング不可

- 見えるのは y(t), setpoint(t), disturbance(t) のみ

制御の成否は、説明ではなく 波形そのものが語ります。

5️⃣ 🎛 AITL-Controller-A-Type

PID × FSM を 実時間制御の中核とし、

NN / RL を 制限付きの実時間適応補助層、

LLM を 非実時間の設計支援層として分離した

AITL アーキテクチャ(A-Type)の最小構成 PoCです。

本 PoC の目的は、

適応・知能を導入しても制御責任を壊さない構造を

最小構成で実証することにあります。

-

PID:

実時間制御のみを担当し、

安定性と基本性能を保証する -

FSM:

劣化検出・状態遷移・モード管理を担当し、

適応を許可するかどうかの最終判断権を持つ -

NN / RL:

FSM によって許可された場合のみ、

実時間で 限定的(bounded)な補助項として介入

(PID 制御を置き換えない) -

LLM:

実時間制御には 一切関与せず、

ログ解析・信頼性評価を通じて

設計レベル(ゲイン・制御方針)の再検討を支援する

非実時間の設計支援層

👉 LLM が制御を置き換えないこと、

👉 NN / RL も PID を置き換えないことを示す最小実証。

- AITL Controller (A-Type) ― 公式アーキテクチャ定義および信頼性境界仕様

▶ インタラクティブ検証(設計者向け Playground)

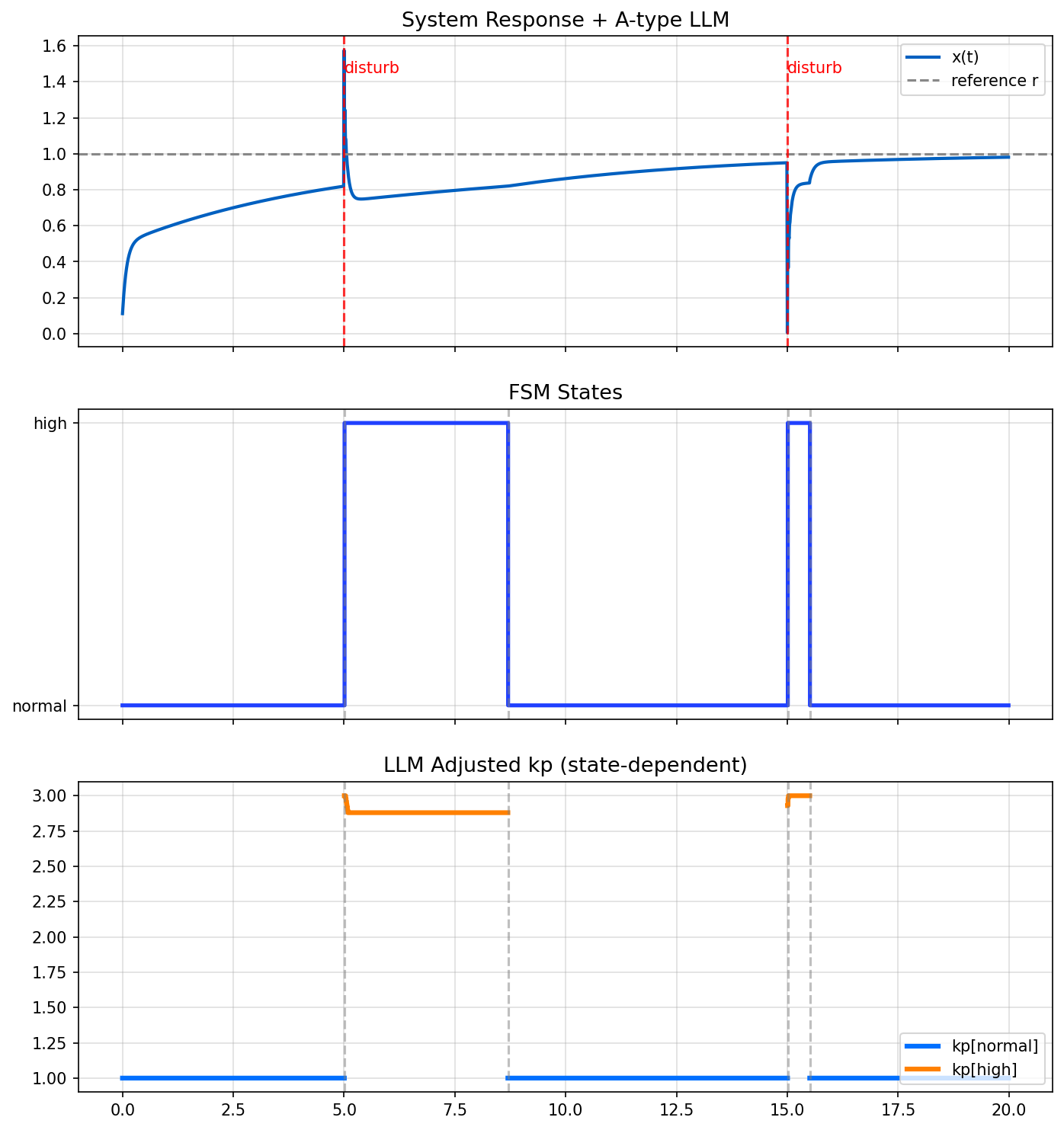

上図は、

AITL(実時間制御:PID × FSM × NN/RL/設計支援:LLM) に基づく

理想化された応答結果(ログ・解析ベース)を示しています。

この責務分離が なぜ必要か、

また どこで適応を止め、設計判断に戻るべきかを

実際に操作しながら確認したい場合は、

以下のインタラクティブ Playground を参照してください。

👉 AITL Control Playground (操作デモ)

- PID ゲインを変更し、安定性・発振・収束を観察

- FSM のモード切替(TRACK / HOLD / MANUAL)を体験

- どの条件で実時間適応(NN / RL)を止め、

設計レベルの再検討(LLM 相当)に戻るべきかを可視化

本ページでは、AITL の

最小構成・責務分離・因果関係の明確化を優先するため、

操作可能なデモは別ページとして分離しています。

🧭 Control Architecture Concepts(制御アーキテクチャ概念)

Runtime(運用)と Design-time(設計)を分離して扱うための

中核となる制御アーキテクチャ概念です。

いずれも 「AIが制御を置き換えない」 ことを前提にしています。

| 概念 | 役割 | リンク |

|---|---|---|

| Envelope Control | 不確実性下において、安全な運転範囲(Envelope)を実行時に拘束する制御概念 | 🔗 Open | 🔧 Repo |

| Design Recovery Control | 破綻・逸脱した制御設計前提を非実時間で回復する設計監督概念 | 🔗 Open | 🔧 Repo |

関係性(非代替・補完関係):

- Envelope Control:「いま、どう抑えて運転するか」 を規定する

- Design Recovery Control:「なぜ設計が通らなくなったか」 を修復する

これらは 競合でも代替でもなく、補完関係にある概念です。

🔔 進行中プロジェクト:AI Control Safety Package

AI Control Safety Package は、

AI / LLM を用いた制御システムを

安全かつ責任ある形で導入するための

設計・レビュー向け実務パッケージです。

本パッケージは、本ポータルで整理している

制御アーキテクチャ概念

(Envelope Control / Recovery Control / AITL)を

実務で使える形に統合することを目的としています。

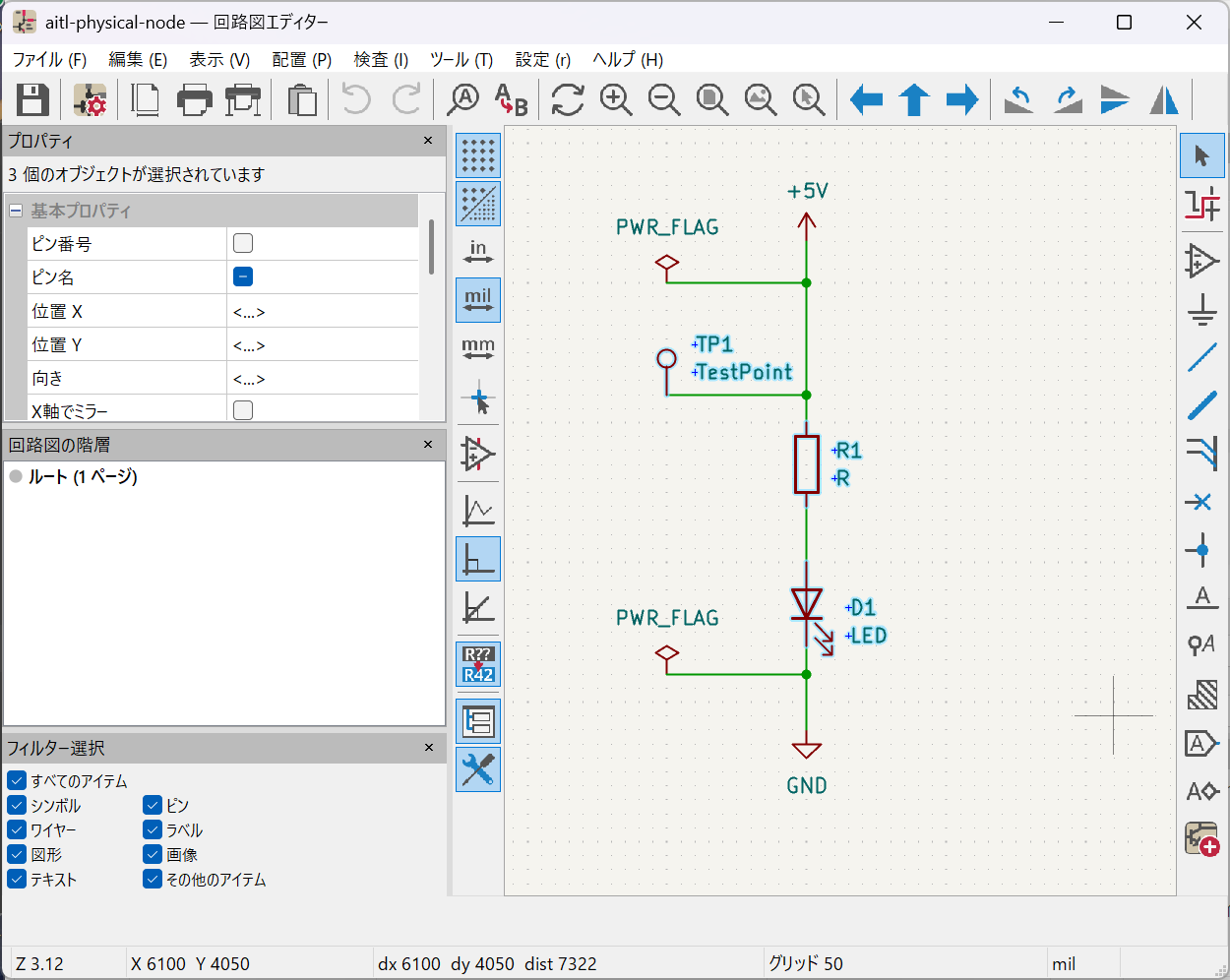

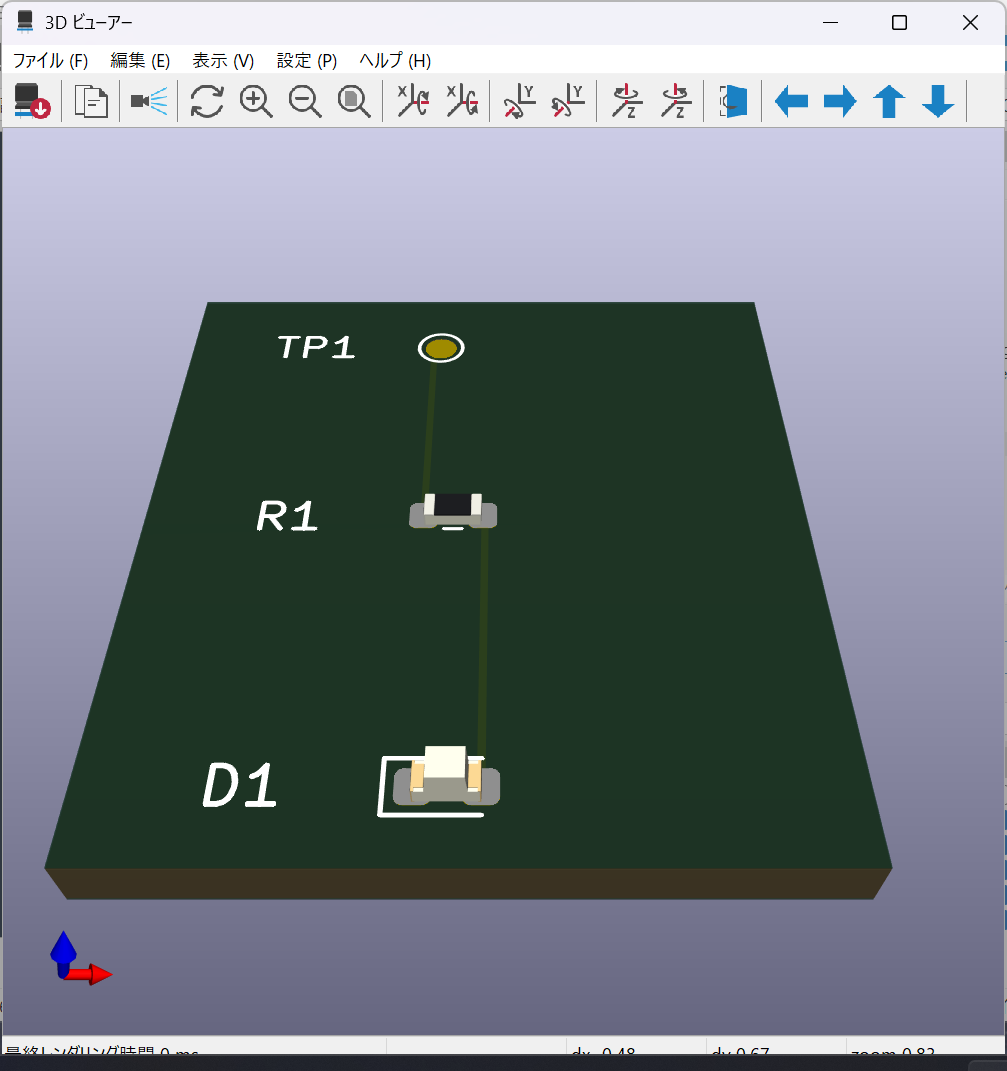

6️⃣ 🧱 Physical Reference PCB (aitl-physical-reference)

抽象的な制御・論理を、実電圧・実電流・実銅配線に固定する

最下層の物理リファレンス基板。

- 抽象ロジックを 測定可能な V–I 挙動へ接地

- LED / R / SW / TP のみで構成された最小物理系

- 制御・AI・FSM・PID の 前提となる物理基盤

👉 「制御以前に、物理がどう存在するか」を示す基準点。

Logic → Physics → Copper

論理状態を、電圧・電流として物理層に固定する

v1 規範回路(Logical–Physical Boundary)。

実部品・銅配線・外形として具現化された

v1 物理リファレンス基板(Physical Truth)。

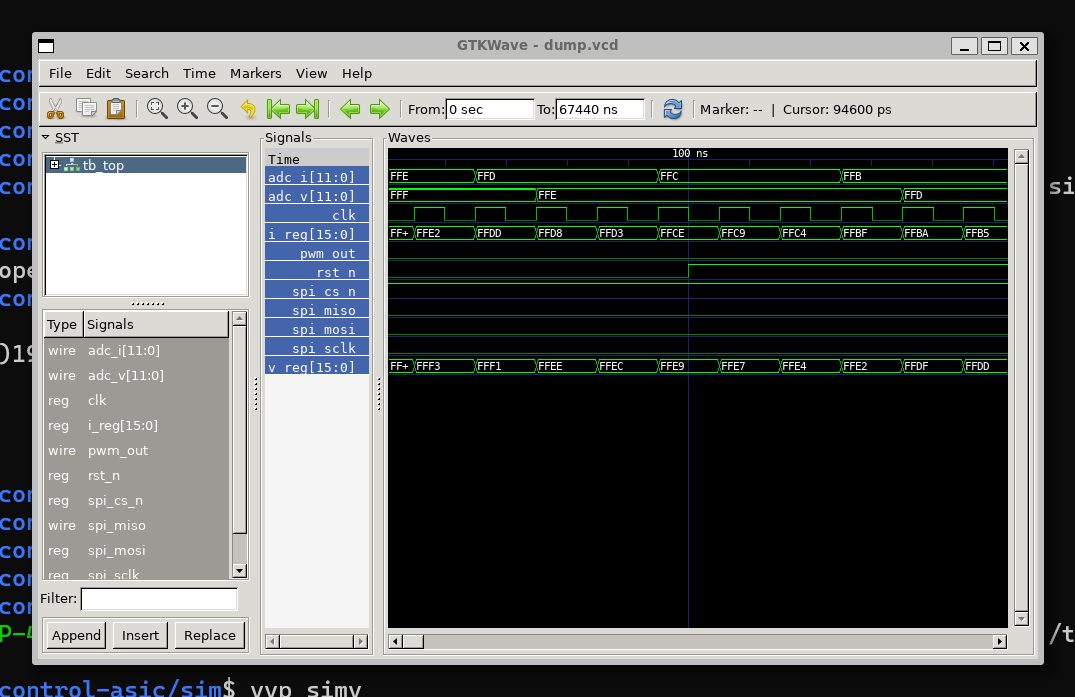

7️⃣ 🧩 V–I Control ASIC on SKY130

V–I 制御(PID + FSM)を RTL → GDS まで一貫実装する ASIC 教材。

- 電圧–電流(V–I)制御を物理量起点で設計

- PID + FSM をハードウェアとして実装

- 制御理論と半導体物理の接続を実証

👉 制御が「物理デバイスにどう実装されるか」を示す教材。

論理検証と物理実装の対応(OpenLane v1)

本教材では、V–I 制御ロジック(PID + FSM)について、

RTL レベルでの機能検証から OpenLane v1 による物理実装までを

一貫したフローとして示しています。

まず論理動作を確認し、その後に物理実装へ進むことで、

制御理論が ASIC 上でどのように具現化されるかを明確にします。

論理検証(GTKWave)

GTKWave による RTL レベルの機能検証。

PID + FSM による制御動作が仕様通りであることを確認。

マクロ内部はブラックボックスとして扱い、制御インタフェースの妥当性に注目しています。

物理実装(OpenLane v1)

OpenLane v1 による標準セル配置・配線のスナップショット。

最終成果物ではなく、設計フロー確認を目的とした途中状態の図です。

※ 本教材では OpenLane v1 を用いて RTL→GDS の一貫フロー成立を実証しています。

マクロ対応を含む発展的な物理設計例は、OpenLane v2 を用いた別教材で扱います。

⚙️ MEMS / Physical Boundary

物理モデルを起点に、抽象化・制御・設計判断を経て、

抽象モデルが通用しなくなる境界としての MEMS 実体に到達する層。

8️⃣ 📐 mems-ana

抽象モデルの限界を確認する pre-FEM MEMS 解析ツール。

- lumped / 簡易モデルが成立する範囲を可視化

- FEM に進む前段階での仮定・近似の妥当性確認

- モデル化誤差が設計判断に与える影響を整理

👉 「どこまで抽象化してよいか」を判断するための前処理ツール。

Demo animation (recommended)

9️⃣ 🖨 Inkjet Technology

インクジェットにおける 物理・駆動・吐出挙動を、

設計判断に必要な因果構造として整理する技術群。

9-1. 💧 Inkjet Printing — Design Trade-off Models

画質・速度・ドット挙動の因果関係を最小モデルで可視化する教材。

- ドット形成・吐出条件・駆動条件の因果関係整理

- 画質 ↔ 速度 ↔ 安定性のトレードオフを明示

- 高忠実度シミュレーションに頼らない設計思考

👉 インクジェット設計の意思決定構造を理解するための教材。

9-2. ⚡ inkjet-timing

ピエゾインクジェットにおける 電気・機械・流体の時間因果関係を、

単一時間軸上で可視化する設計・教育用デモ。

- 電圧駆動 → 機械変形 → 流体応答の時間順序を可視化

- 遅延・重なり・非同期要素の影響を理解

- 波形設計と吐出挙動の関係を直感的に把握

👉 マルチフィジクスを「時間因果」として捉えるためのデモ。

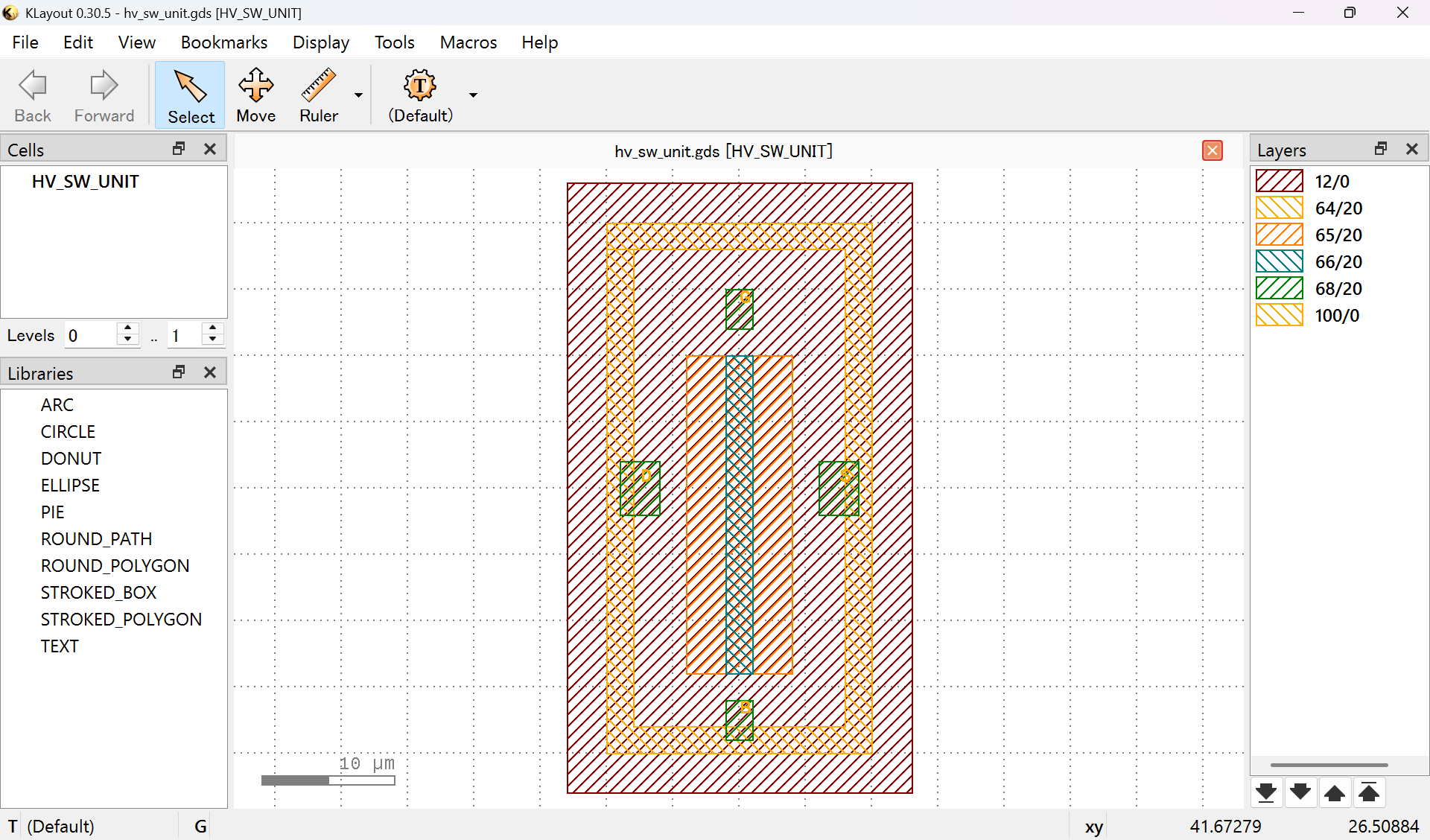

9-3. 🧱 Inkjet Driver IC — Physical Interface Abstraction

インクジェット駆動ICが MEMS/流体世界と接続する物理的境界を、

PDK・プロセス前提込みで定義する設計ノード。

本プロジェクトは GF180 PDK を前提とし、

インクジェット駆動に必須となる 高耐圧(HV)MOS を手動レイアウトで設計する。

(※ sky130 のような標準セル+自動合成前提とは異なる)

本ノードで定義すること

- MEMS/流体モデルから ICが受け取る等価負荷(V–I–t 条件)

- それを IC側の電圧・電流・信頼性制約へ翻訳

- 抽象モデル ⇄ 実レイアウト(HVMOS/DNWELL/配線/パッド)の対応

- 「どこから先は IC では制御できないか」の明確化

👉 物理モデルと IC 設計の 責任分界点を定義するための設計インタフェース。

HVMOSレイアウトによる物理インタフェース実体

以下に示す図は、インクジェット駆動ICが MEMS/流体世界と接続する 物理的インタフェースの実体としての 高耐圧MOS(HVMOS)レイアウト例である。

ここでは、単体デバイスではなく、 実際にICとして外界に提示される最小構造である HV_SW_UNIT(HVMOS+DNWELL+ガードリング) を代表例として示す。

🔟 🛠️ Full Code Mechanical Design(コード駆動型機械設計)

機械・MEMS 構造を、GUI 操作ではなく

「実行可能なコード」として定義する設計方法論。

本プロジェクトでは、CAD を単なる作図ツールではなく、

物理構造および設計意図を実行・検証するエンジンとして扱う。

- 幾何形状は Python コードにより生成される

- 寸法・配置は設計意図として明示的に記述される

- アセンブリは拘束解決ではなく、配置(placement)として定義される

- CAD ファイル(FCStd / STEP 等)は最終成果物ではなく 副生成物とみなす

この方法論により、

機械・MEMS 構造は 再現可能・レビュー可能・自動化可能となり、

物理境界条件として 制御・AITL 上位層と明示的に接続できる。

👉 Full Code Mechanical Design は、

Samizo-AITL における

「物理構造を設計資産として固定化するための基盤方法論」である。

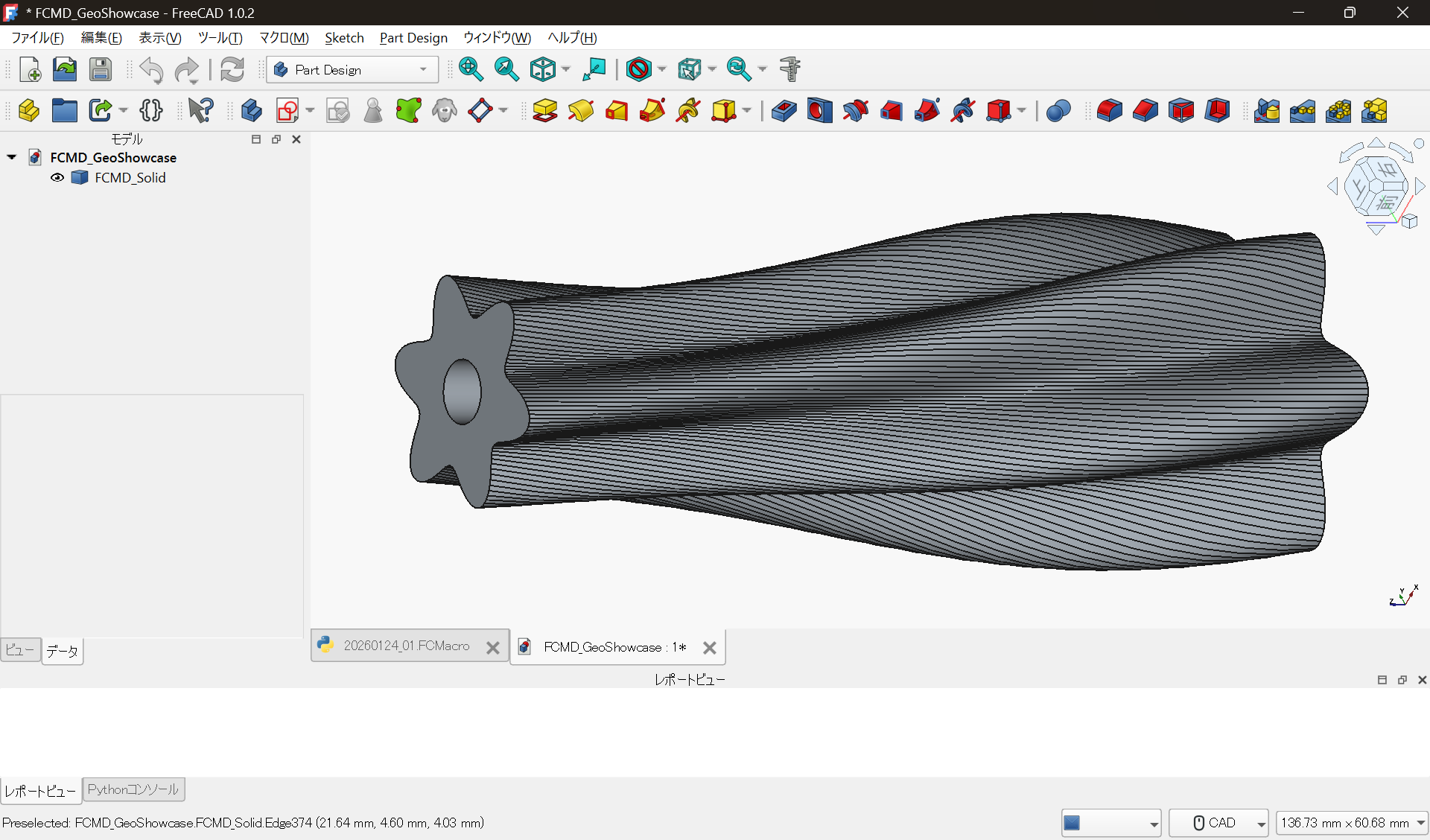

📐 Advanced Geometry Examples(実行可能な設計意図)

この例は、GUI 操作を用いず、Python コードのみで生成された

ツイスト付きロフト立体構造である。

- 断面形状・配置・回転量は すべてコード上で明示的に定義

- FreeCAD は作図ツールではなく 幾何生成エンジンとして使用

- 形状は再実行・再生成可能で、設計意図がコードとして保存される

これは、CAD ファイルを成果物とせず、

設計コードそのものを一次設計資産とする

Full Code Mechanical Design の考え方を示す代表例である。

🎞 AITL Animation Demos

PID 制御・FSM・LLM を含む AITL 構造や、

物理・デバイス・マルチフィジクス挙動を

アニメーションとして可視化したデモ集。

- PID 制御の時間応答および制御フローの可視化

- AITL における各レイヤ(PID / FSM / NN・RL / LLM)の役割分担の確認

- インクジェット、MEMS、デバイス物理における時間・空間挙動の把握

数式やコードに入る前段として、

振る舞いと構造を時間軸上で把握することを目的とする。

🎞 AITL Control Flow Demo

本デモは、AITL における制御アーキテクチャ、すなわち

PID × FSM を実時間制御核とし、

NN / RL(実時間適応補助)および LLM(非実時間再設計)を分離した階層構造が、

時間軸上でどのように連携するかを示す。

🔁 各レイヤの役割(要点)

-

PID(実時間制御)

実時間制御を一貫して担当し、

通常状態では PID のみで安定追従を行う。 -

FSM(監督・判断)

状態監督を担当し、誤差や劣化を検出する。

状態遷移(monitoring / disturbance / recovery / stable)を管理し、

実時間適応や再設計を許可するかどうかを判断する。 -

NN / RL(実時間適応補助)

FSM により許可された場合のみ介入し、

実時間で限定的(bounded)な補助項として動作する。 -

LLM(非実時間設計支援)

FSM により呼び出された場合に限り、

ログ解析や信頼性評価を通じて

設計レベル(例:PID ゲイン、制御方針)の再検討を支援する。

📉 デモの流れ

- 通常状態:PID による追従制御、FSM は監視のみ

- 外乱発生:誤差増大を FSM が検出

- 適応(条件付き):FSM の許可下で NN / RL が限定的に介入

- 再設計(必要時):FSM が LLM を呼び出し設計レベルの検討を実施

- 回復:PID による再追従、FSM は stable 状態へ遷移

※ 本デモでは、外乱が PID + FSM の範囲で回復可能なため、 NN / RL および LLM は起動せず、 「起動しないこと自体」が責務分離の例として示される。

🎯 このデモで確認できること

本デモでは、AITL における責務分離が

時間軸上でどのように維持されるかを確認できる。

- 実時間制御は PID が担当し続ける

- FSM が状態監督と介入判断を行う

- NN / RL は補助的役割に限定される

- LLM は非実時間の設計支援に限定される

各レイヤは互いに代替せず、

制御責任が崩れない構造として分離されている。

🎓 AITL Training & Competence Framework(教育・訓練)

Samizo-AITL の設計思想および技術体系を

組織的に教育・訓練・検証するための独立したドキュメント群です。

本フレームワークは、

ISO 9001 Clause 7.2(Competence)を想定し、

AITL における責務分離(PID / FSM / NN・RL / LLM)を

教育・力量管理の観点から明文化しています。

👉 AITL Training GitHub Page and Repository

- 技術実装は含みません

- 教育方針・訓練計画・検証・記録を定義します

- Samizo-AITL 本体は Single Source of Truth のまま維持されます

👤 Author

三溝 真一(Shinichi Samizo)

独立系半導体研究者

- GitHub: https://github.com/Samizo-AITL

- Zenn: https://zenn.dev/samizo_aitl

- Qiita: https://qiita.com/ctr_bug

- Career Summary: https://samizo-aitl.github.io/about/career-summary/

🔐 利用条件とライセンスについて(ハイブリッド方式)

本ポータルは ハイブリッドライセンス方式を採用しています。

| 📌 項目 | ライセンス | 説明 |

|---|---|---|

| 💻 ソースコード | MIT License | 自由に使用・改変・再配布可能 |

| 📄 テキスト教材 | CC BY 4.0 または CC BY-SA 4.0 | 出典明記必須(BY-SA は継承条件あり) |

| 📊 図・ダイアグラム | CC BY-NC 4.0 | 非商用利用に限定 |

| 🔗 外部参照資料 | 元ライセンスに従う | 出典を適切に明記すること |

⚠️ AITL アーキテクチャおよび方法論に関する重要な注意

上記ライセンスは、

個々の素材(コード・文章・図表)に対して適用されるものです。

AITL アーキテクチャおよび方法論を一体の体系として利用すること

(FSM × PID × LLM による層構造制御設計およびその教育体系)は、

上記ライセンスによって 包括的に許諾されているものではありません。

🚫 AITL 方法論全体の体系的な再利用、再配布、

または 商用利用を行う場合は、

事前にプロジェクト作者の許可が必要です。

💬 技術ディスカッション / Technical Consultation

本ポータルでは、メールや SNS 等の私的な連絡手段は設けていません。

技術的な議論・相談・協業に関する問い合わせは、

GitHub Discussions 上での公開議論として受け付けています。設計思想の共有、因果構造の整理、PoC 検討など、

再現性と技術的文脈を重視した対話を目的としています。