BSIM4_ANALYZER_DIM

Links

| Language | GitHub Pages 🌐 | GitHub 💻 |

|---|---|---|

| 🇺🇸 English |  |

|

Automatic BSIM4 Analysis Tool for CMOS 130nm DIM (L/W Sweep)

⚡ DIM-based model generation with Short-Channel Effects (SCE) + Fully Automated Analysis Flow

📘 Overview

BSIM4_ANALYZER_DIM is a Python + ngspice environment for performing automatic L/W sweep analysis

of MOSFET Vg–Id and Vd–Id characteristics based on BSIM4 models.

The tool generates netlists, runs ngspice, extracts model parameters, and outputs plots fully automatically.

In addition, the DIM model generation step incorporates Short-Channel Effects (SCE), enabling realistic

130nm device behavior:

- Vth roll-off

- DIBL

- Mobility degradation

- Ion / Ioff dependence on L & W

This enables dimension-aware device modeling for education, research, and standard-cell engineering.

📁 Directory Structure

BSIM4_ANALYZER_DIM/

│

├─ models/

│ ├─ 130nm_nmos_lxxx.sp

│ ├─ 130nm_nmos_wxxx.sp

│ ├─ 130nm_pmos_lxxx.sp

│ └─ 130nm_pmos_wxxx.sp

│

├─ templates/

│ ├─ template_vg_dim.cir

│ └─ template_vd_dim.cir

│

├─ run/

│ ├─ run_vg_dim.py

│ └─ run_vd_dim.py

│

├─ plot/

│ ├─ plot_vg_dim.py

│ └─ plot_vd_dim.py

│

└─ results/

└─ 130nm/

├─ l_vg/

├─ w_vg/

├─ l_vd/

└─ w_vd/

⚙ Analysis Conditions

Temperature

- RT = 25°C

Technology

- CMOS 130nm

L Sweep (W = 1 µm fixed)

0.10, 0.13, 0.16, 0.20, 0.50, 1.00 µm

W Sweep (L = 0.13 µm fixed)

0.50, 1.00, 2.00, 5.00, 10.00 µm

Both NMOS and PMOS are fully analyzed.

🚀 How to Run

■ Vg–Id Sweep

python run/run_vg_dim.py

■ Vd–Id Sweep

python run/run_vd_dim.py

📊 Example Output Files

From:

results/130nm/l_vg/

You will see files such as:

130nm_nmos_L013_vg.cir

130nm_nmos_L013_vg.dat

130nm_nmos_L013_vg.csv

130nm_nmos_L013_vg.log

130nm_nmos_L013_vg.png (generated by plot_vg_dim.py)

🧩 Template Specifications

■ template_vg_dim.cir

- Gate sweep (

.dc VG) - Uses

wrdatato store Vg and Id - Automatically unifies NMOS/PMOS current sign

■ template_vd_dim.cir

- Drain sweep (

.dc VDSRC) - NMOS: Id = I(d) (positive direction)

- PMOS: Id sign inverted to match NMOS convention

📈 Extracted Parameters

■ From Vg–Id

- Vth_gmmax — threshold voltage using gm-maximum method

- gmmax — peak transconductance

■ From Vd–Id

- Id_lin — linear-region current

- Id_sat — saturation-region current

- Vdsat_approx — approximate Vdsat based on curvature change

🔬 DIM Model Generation with SCE Effects

generate_dim_models.py adjusts BSIM4 parameters based on device dimensions (L & W)

to reproduce short-channel physics realistically.

✔ Vth Roll-off

- Shorter L → reduced VTH0

✔ DIBL

Enhanced:

- PDIBLC1, PDIBLC2, ETA0 for short-channel devices

✔ Mobility Degradation

- U0 reduced for shorter L

- VSAT increased to reflect faster saturation behavior

✔ Narrow-Width Effect

- Smaller W increases Vth

- W-dependent adjustment of VTH0 and RDSW

These adjustments produce realistic L/W dependence of:

- Ion / Ioff

- Vth

- gm

- Vd–Id curves

📘 Why DIM Analysis Is Important

The framework enables exploration of:

- Short-Channel Effects (SCE)

- DIBL behavior

- Vth roll-off

- gm dependence on L/W

- Ion / Ioff variation

- SRAM β ratio design

- Standard-cell drive strength

- Process/device education and training

📎 Reference Examples (Screenshots)

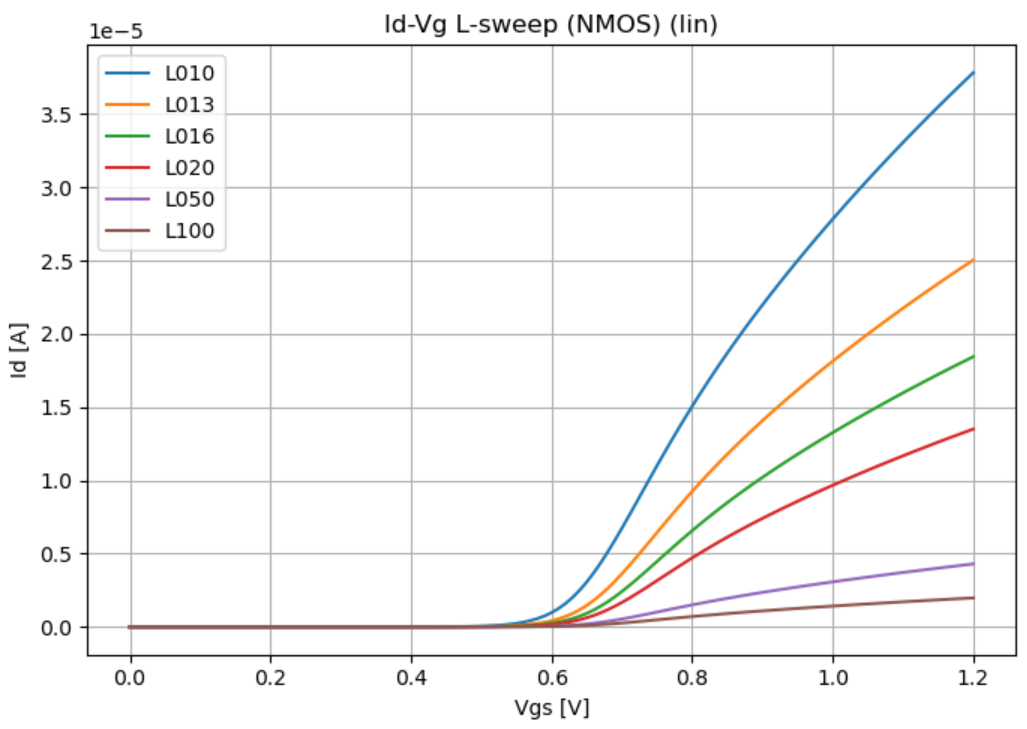

■ Vg–Id (L Sweep, NMOS, Linear)

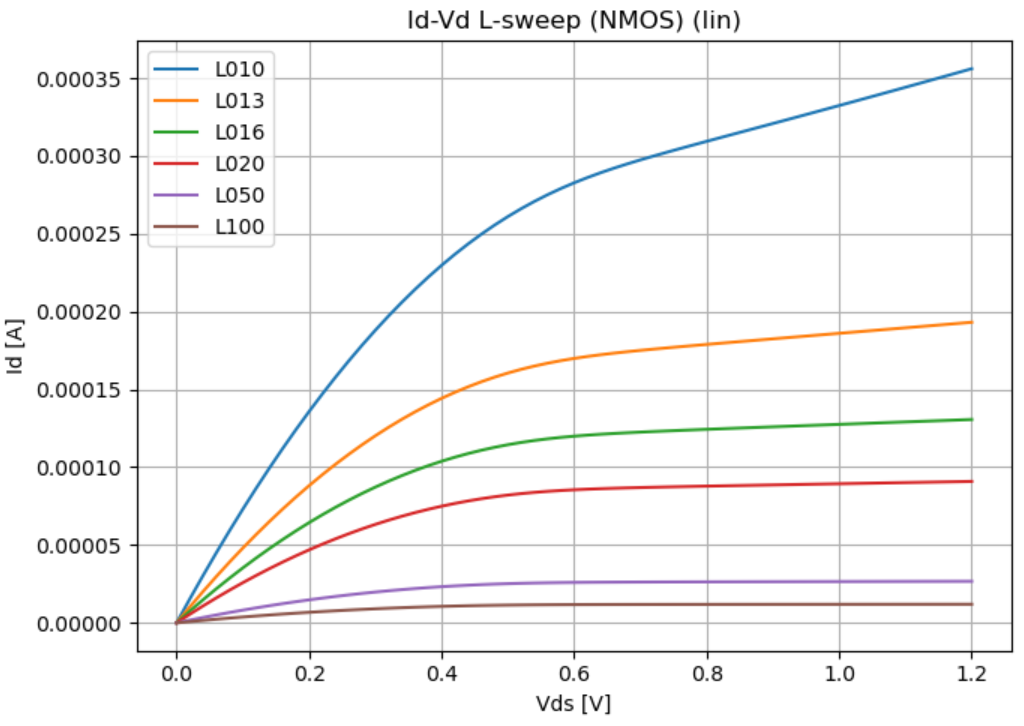

■ Vd–Id (L Sweep, NMOS, Linear)

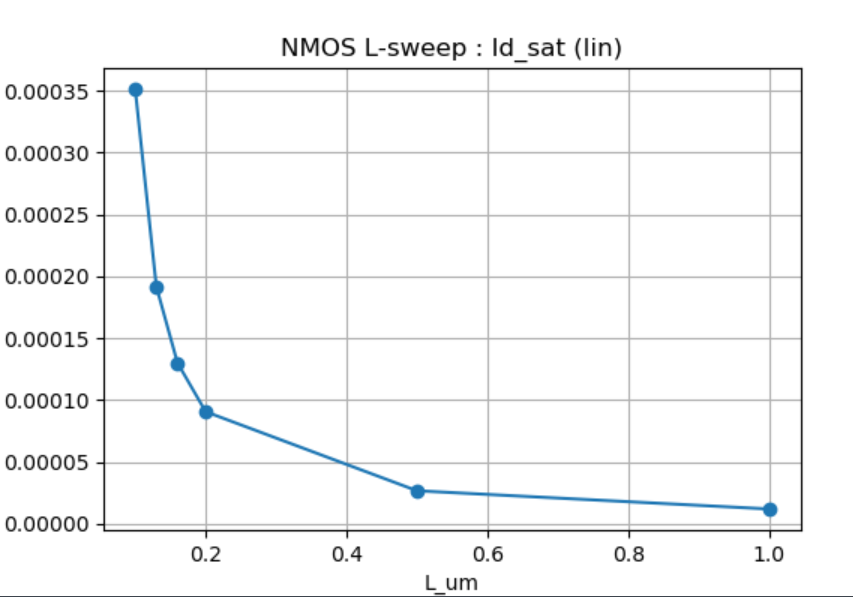

■ L vs. Id_sat (NMOS)

🗂 Version

Version: 1.0 (DIM Base / SCE Adjusted)

Last Update: 2025-01

👤 Author

| Item | Details |

|---|---|

| 👨🔬 Name | Shinichi Samizo |

| 💻 GitHub | Samizo-AITL |

📄 License

| Component | License | Notes |

|---|---|---|

| 💻 Source Code | MIT License | Free use / modification |

| 📄 Text Materials | CC BY 4.0 / CC BY-SA 4.0 | Attribution required |

| 🎨 Figures & Diagrams | CC BY-NC 4.0 | Non-commercial only |

| 🔗 External References | Original license | Proper citation required |